| [54] | MULTI-CHIP CALCULATOR SYSTEM     |

|------|----------------------------------|

|      | HAVING CYCLE AND SUBCYCLE TIMING |

|      | GENERATORS                       |

[75] Inventors: Michael J. Cochran, Richardson;

Charles P. Grant, Jr., Dallas, both

of Tex.

[73] Assignee: Texas Instruments Incorporated,

Dallas, Tex.

[22] Filed: Sept. 13, 1973

[21] Appl. No.: 397,060

[58] Field of Search .......... 235/152, 156; 340/172.5

[56] References Cited UNITED STATES PATENTS

3.798.606 3/1974 Henle et al. ..... 340/172.5 3,800,129 3/1974 Umstattd ...... 235/156 Primary Examiner-David H. Malzahn Attorney, Agent, or Firm-Harold Levine; Rene E. Grossman; Thomas G. Devine

## [57] **ABSTRACT**

An electronic protable calculator implemented in integrated circuit semiconductor technology utilizes cycle and subcycle timing generators on both the arithmetic chip and on the memory chip. One output terminal conveys both an internal operating condition of the arithmetic to other semiconductor calculator chips in the system including to the memory chip, and also conveys timing synchronization for the cycle and subcycle timing generators on the memory chip. The arithmetic chip also has means for generating a multibit command signal comprising a first set of bits representing internal conditions of the arithmetic chip and a second set of bits selectively representing a memory address location dependent upon bits in the first set.

## 13 Claims, 81 Drawing Figures

SHEET 1 63

SHEET 2 63

SHEET 3 63

SHEET 4 63

SHEET 5 63

Fig. 5c

SHEET 8 63

Fig. 6a

Fig. 7

. SHEET 12 63

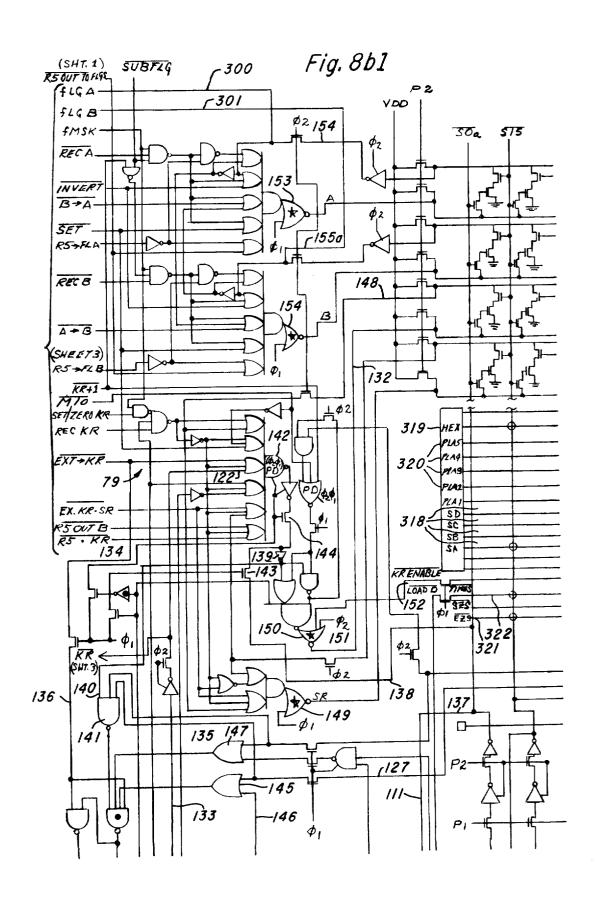

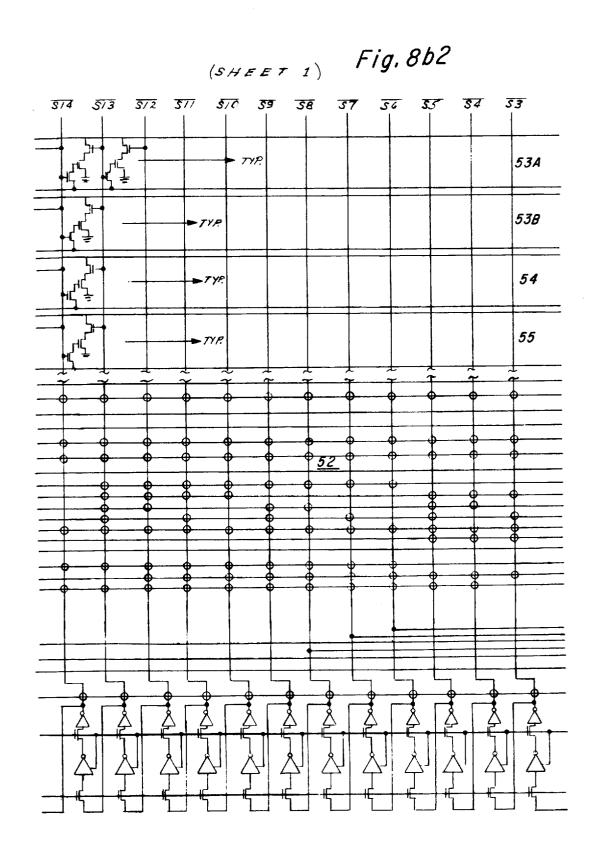

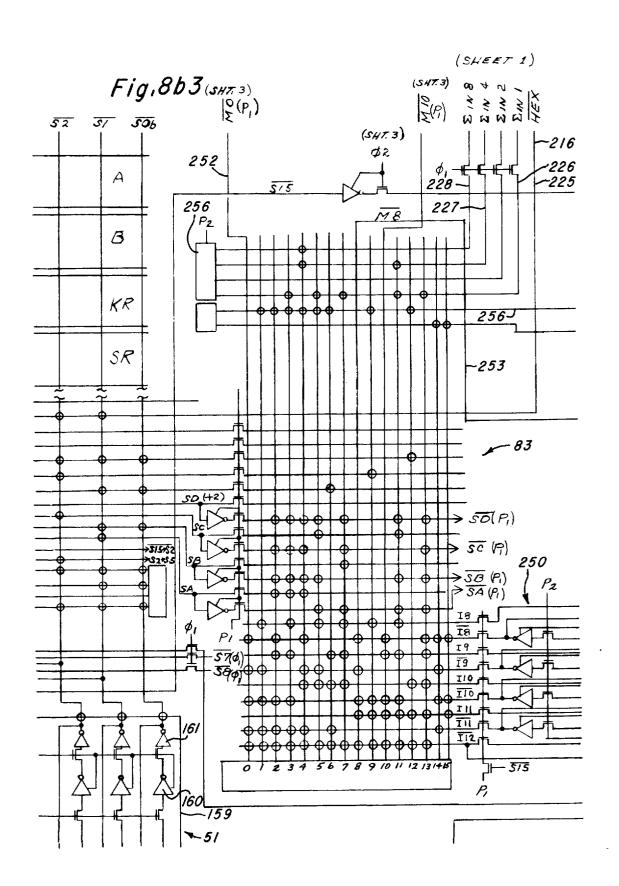

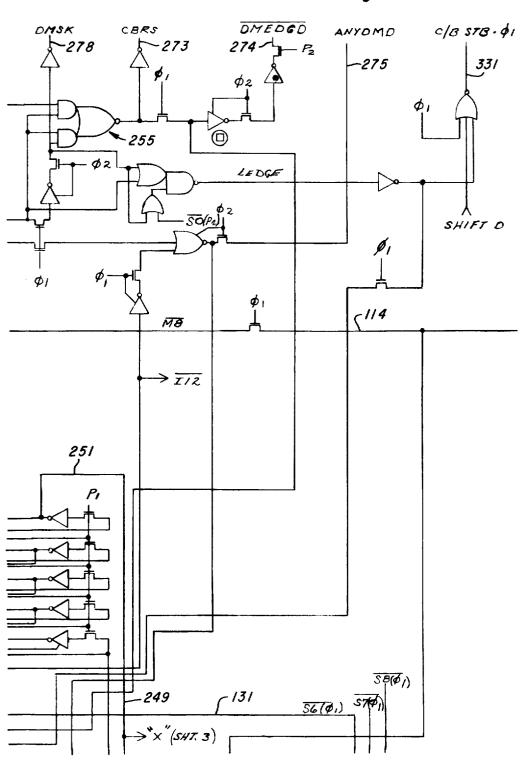

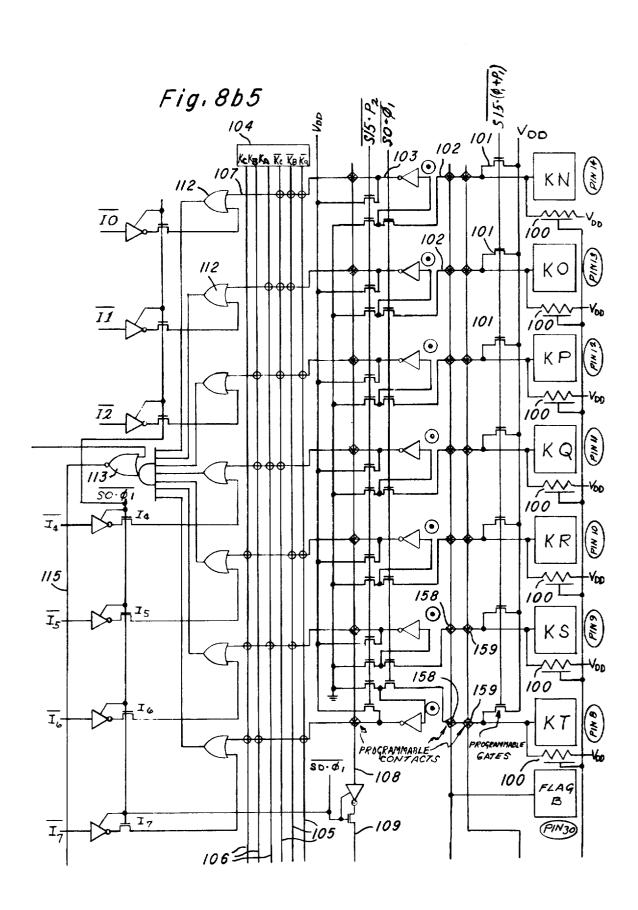

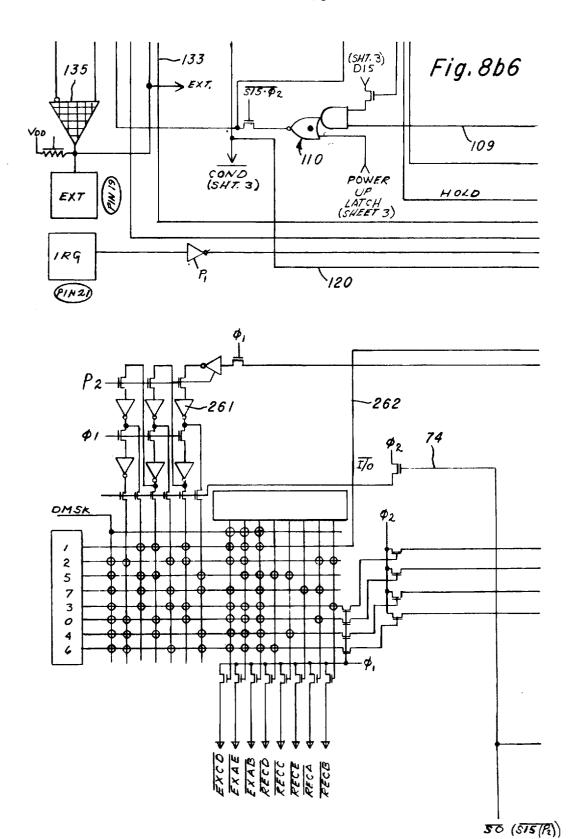

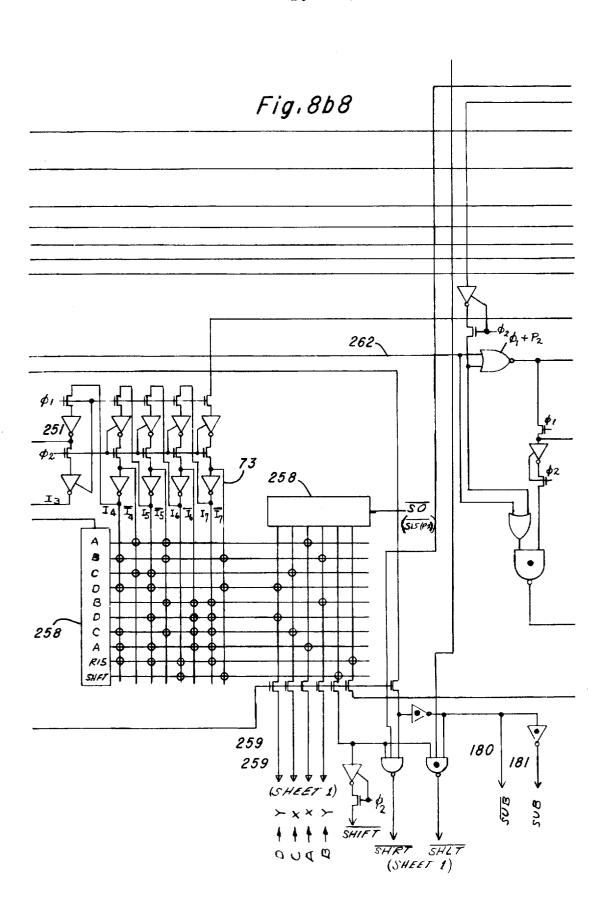

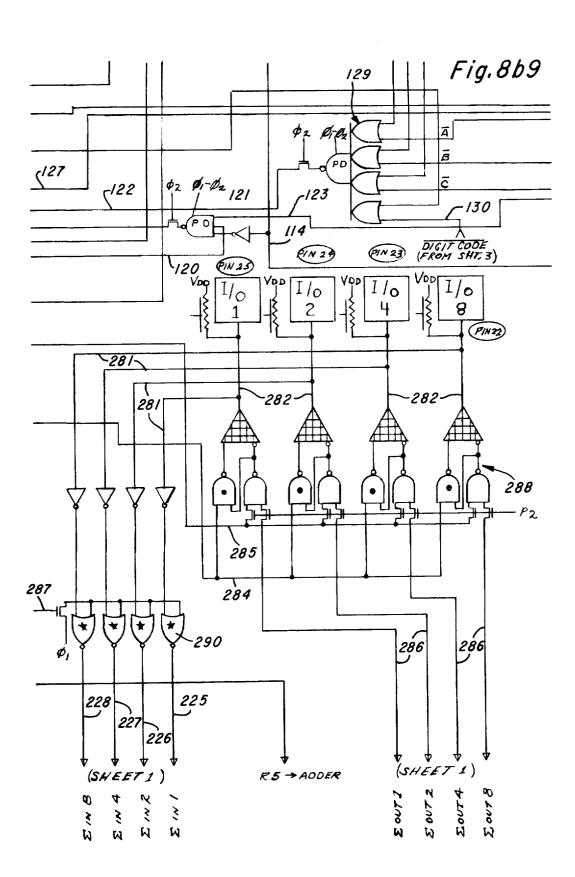

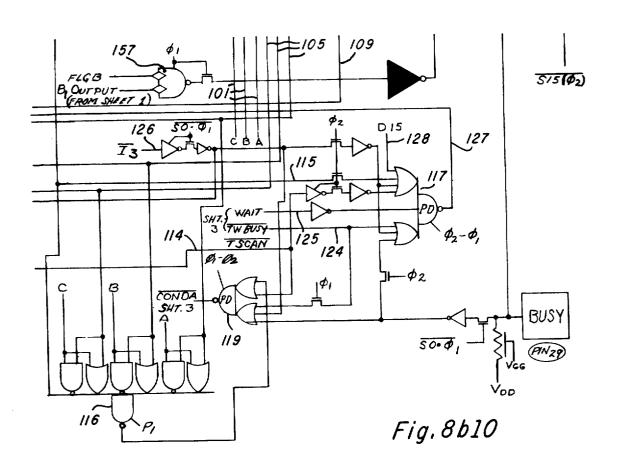

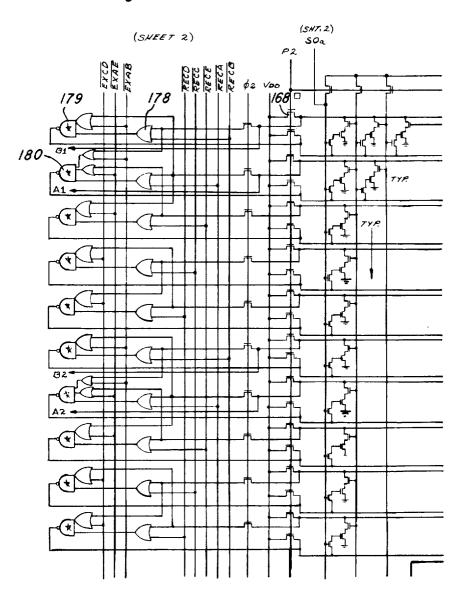

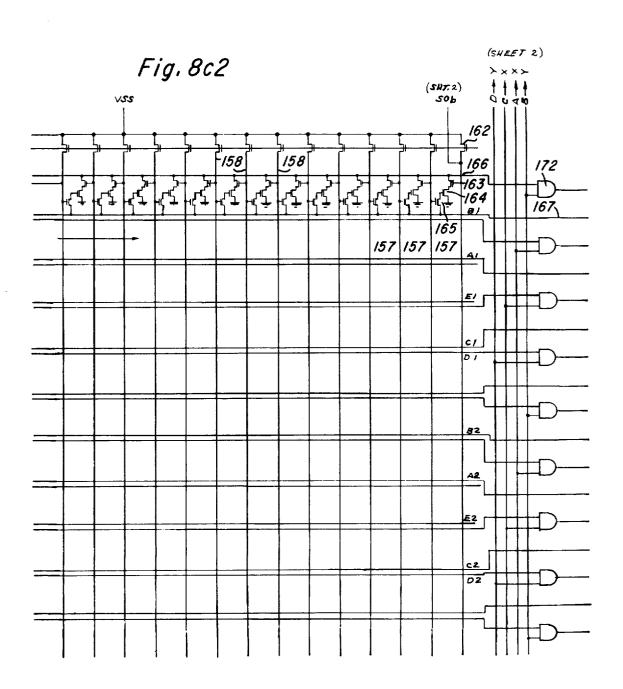

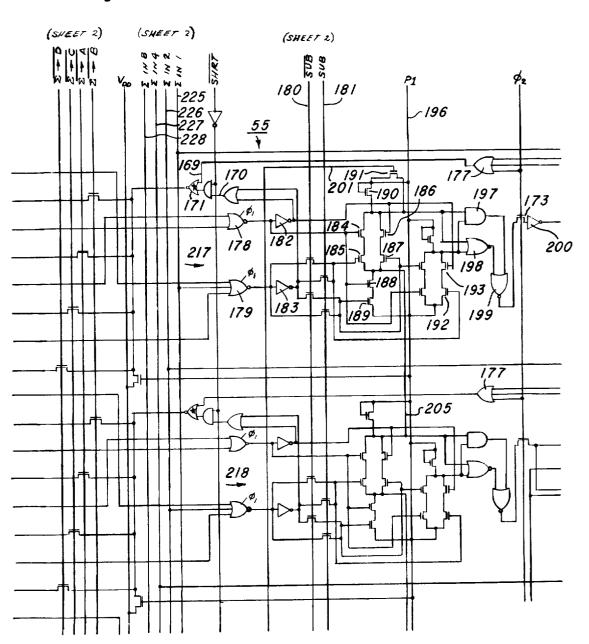

| Fig. 8b1 | Fig. 8b2 | Fig. 8b3 | Fig. 8b4 | Fig. 8b5  |

|----------|----------|----------|----------|-----------|

| Fig. 8b6 | Fig. 8b7 | Fig. 8b8 | Fig. 8b9 | Fig. 8b10 |

Fig. 8a

| Fig. 8cl | Fig. 8c2 | Fig. 8c3 | Fig. 8c4 |

|----------|----------|----------|----------|

| Fig. 8c5 | Fig. 8c6 | Fig. 8c7 | Fig. 8c8 |

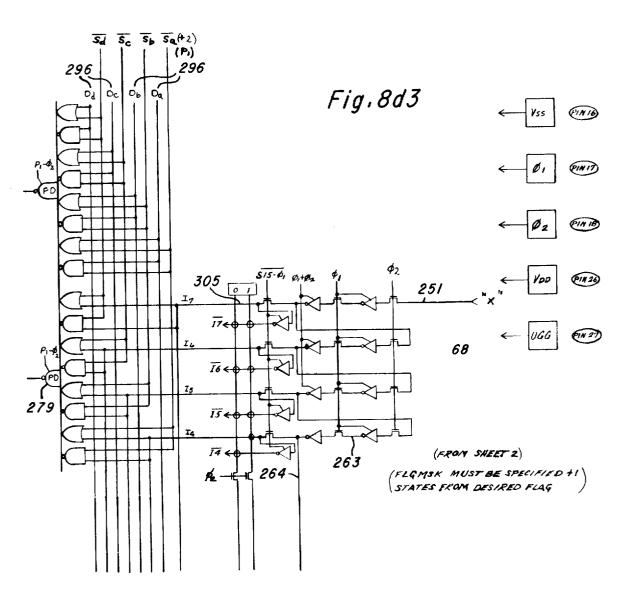

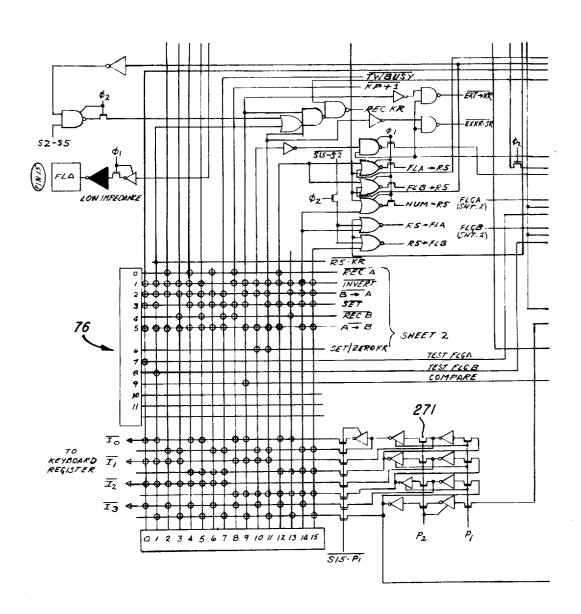

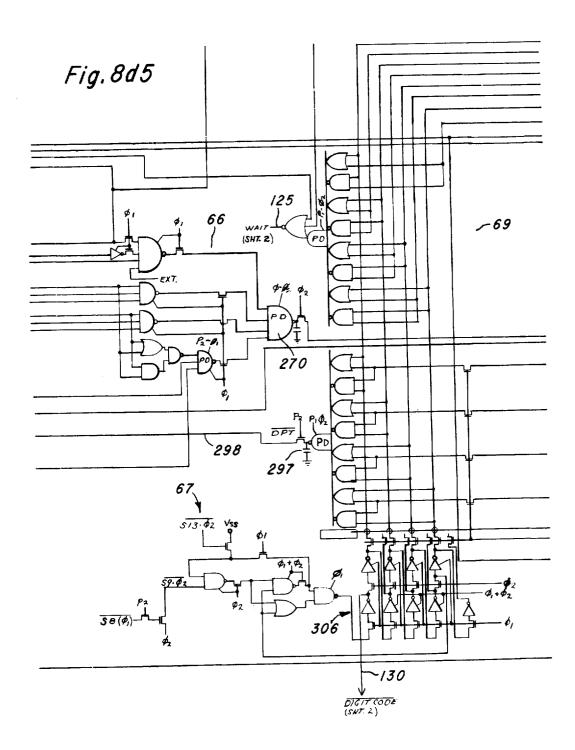

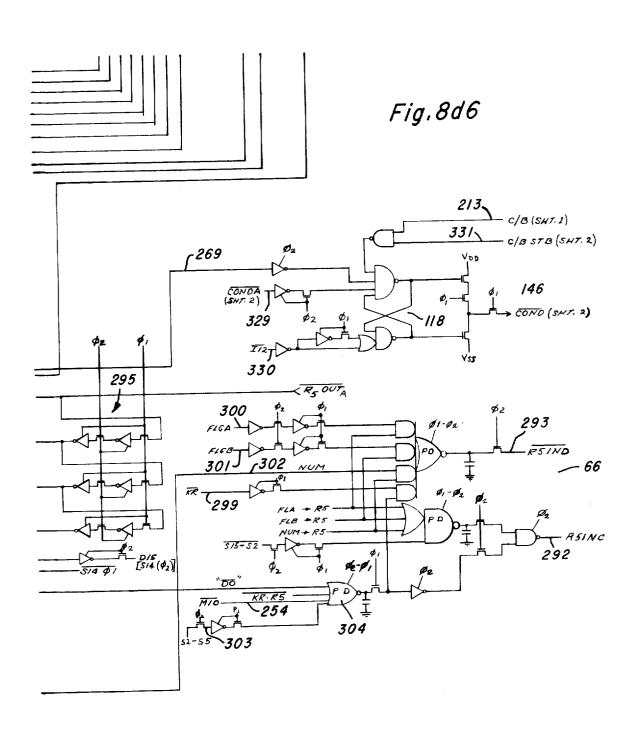

| Fig. 8d1 | Fig. 8d2 | Fig. 8d3 |

|----------|----------|----------|

| Fig. 8d4 | Fig. 8d5 | Fig. 8d6 |

SHEET 13 63

SHEET 15 63

SHEET 18 63

Fig.8b4

SHEET 18 63

| F   | Fig.8b7                                                                          |  |

|-----|----------------------------------------------------------------------------------|--|

|     |                                                                                  |  |

|     |                                                                                  |  |

|     |                                                                                  |  |

|     |                                                                                  |  |

|     |                                                                                  |  |

|     |                                                                                  |  |

|     |                                                                                  |  |

| 260 |                                                                                  |  |

|     | Ø.e                                                                              |  |

|     |                                                                                  |  |

|     | $(\frac{\overline{S15}}{\overline{S14(P_2)}})$                                   |  |

|     | $\frac{\left(\overline{SI}+(P_1)\right)}{SO}$ $\left(\overline{SI}+(P_2)\right)$ |  |

|     |                                                                                  |  |

|     |                                                                                  |  |

|     |                                                                                  |  |

|     |                                                                                  |  |

|     | $\phi_l - c_l$                                                                   |  |

|     | (SHEET 1) VSUBFIG                                                                |  |

|     |                                                                                  |  |

SHEET **20** €3

SHEET 22 63

SHEET 23 63

Fig. 8c1

SHEET 24 63

SHEET 25 63

Fig.8c3

Fig. 8c4

SHEET 27 63

Fig. 8c5

. SHEET 28 63

Fig. 8c6

SHEET 29 63

Fig.8c7

Fig.8c8

SHEET 31 63

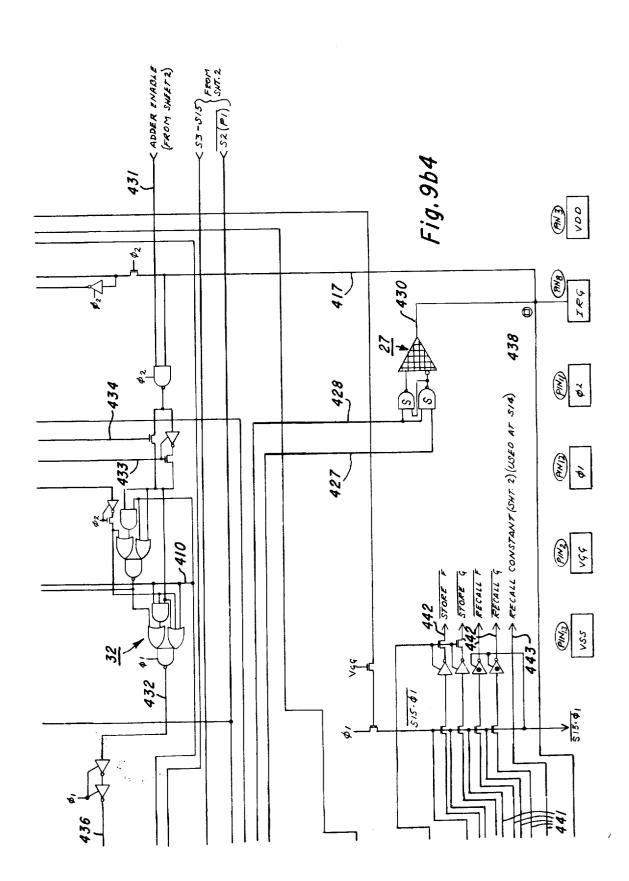

| Fig. 9bl | Fig. 9b2 |

|----------|----------|

| Fig. 9b3 | Fig. 9b4 |

Fig.9a

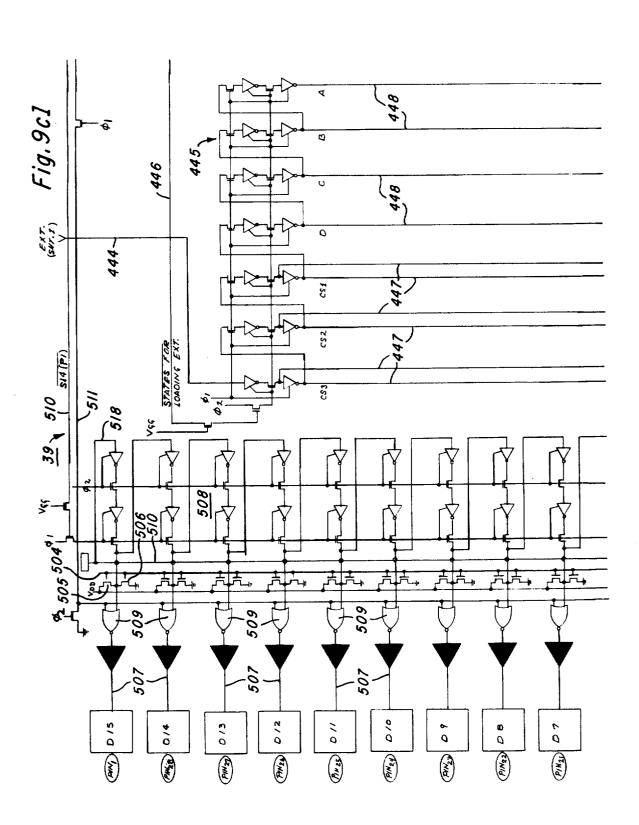

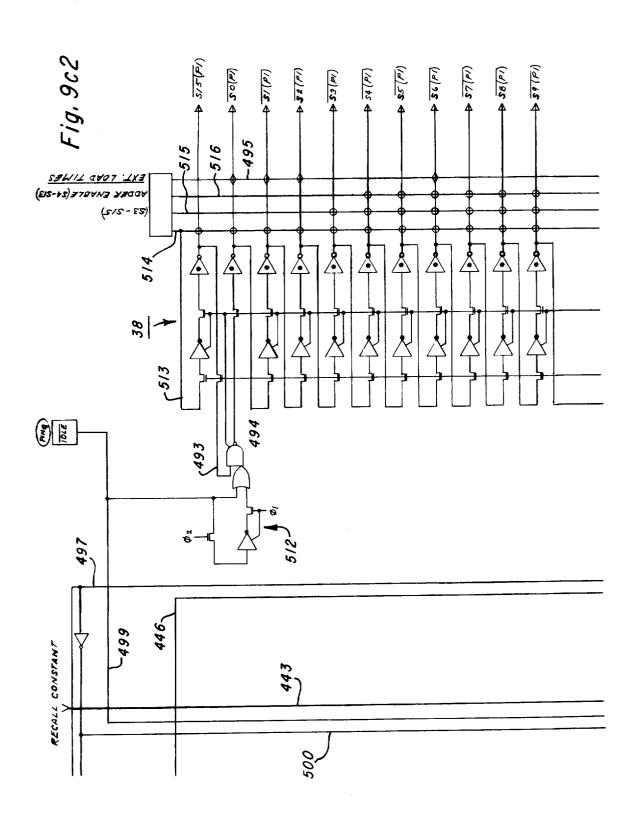

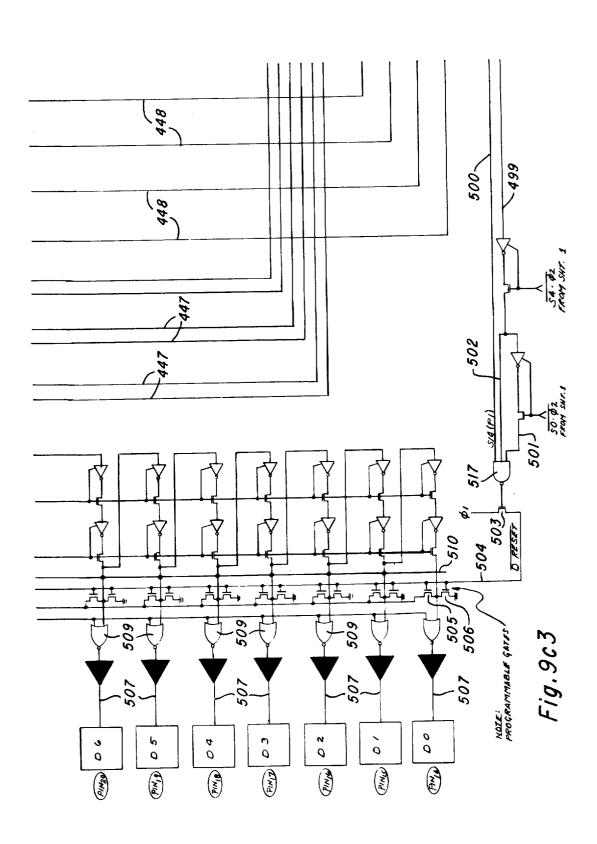

| Fig. 9c1 | Fig. 9c2 |

|----------|----------|

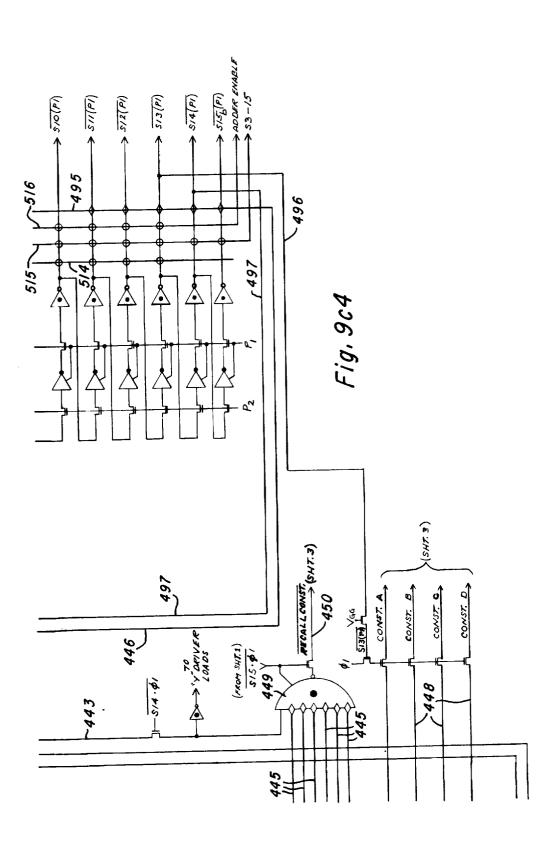

| Fig. 9c3 | Fig. 9c4 |

| Fig. 9dl | Fig. 9d2 | Fig. 9d3 | Fig. 9d4 |

|----------|----------|----------|----------|

| Fig. 9d5 | Fig. 9d6 | Fig. 9d7 | Fig. 9d8 |

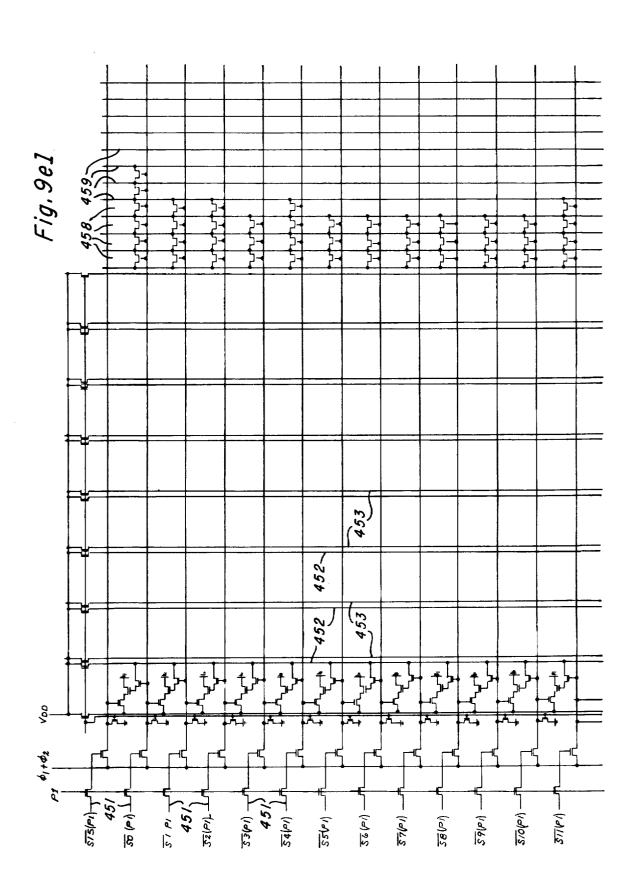

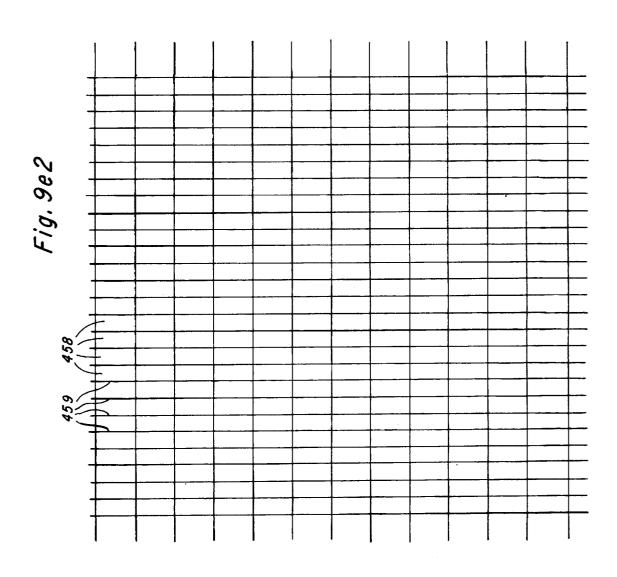

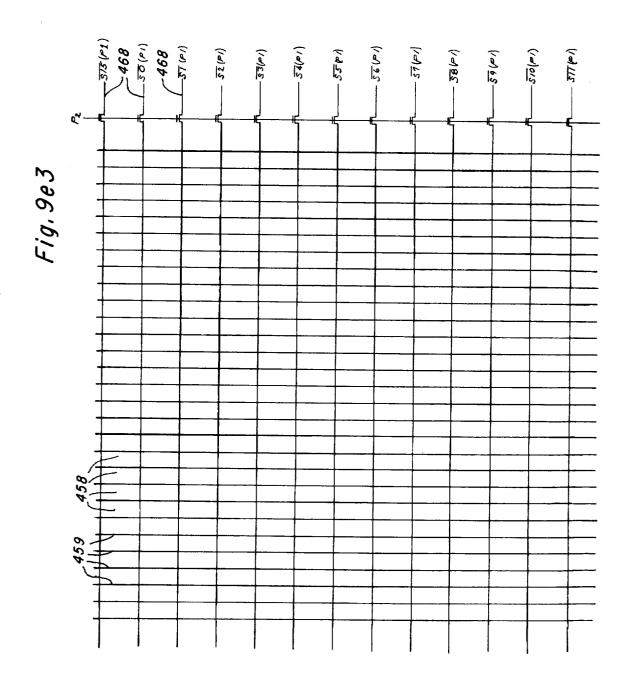

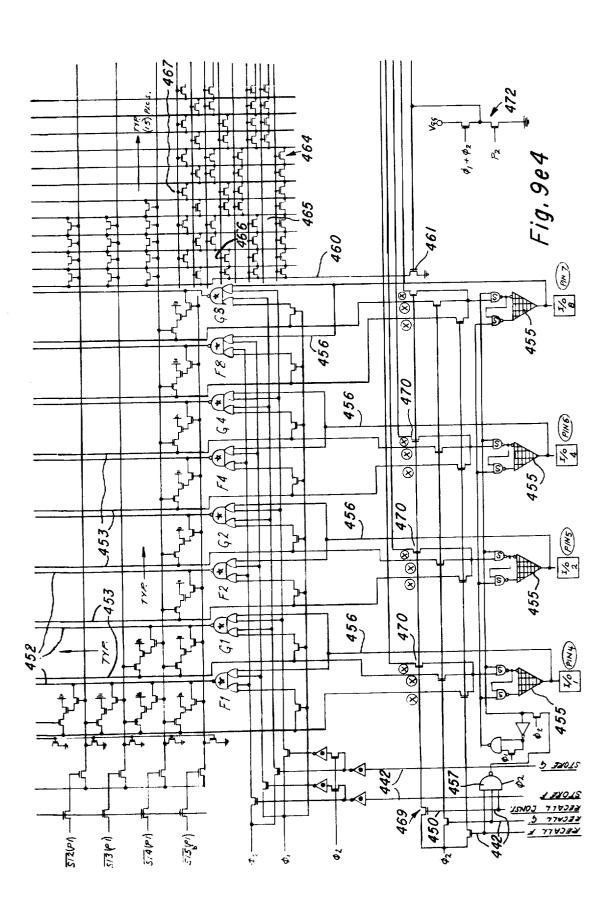

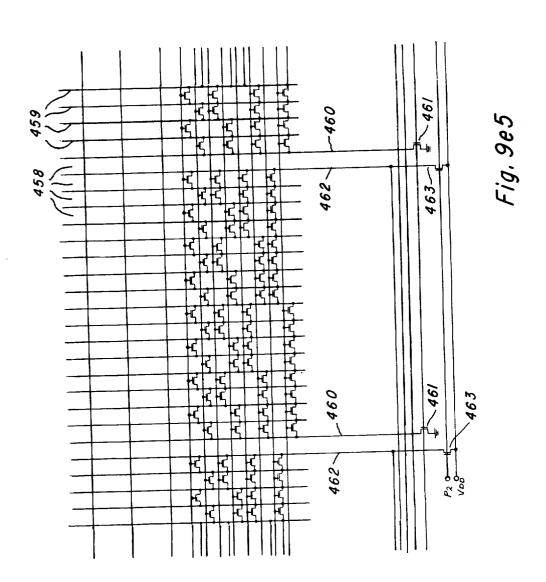

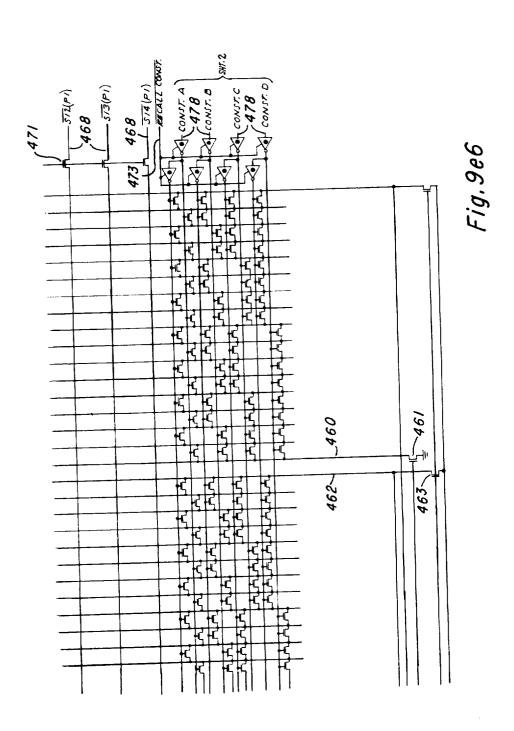

| Fig. 9el | Fig. 9e2 | Fig. 9e3 |

|----------|----------|----------|

| Fig. 9e4 | Fig. 9e5 | Fig. 9e6 |

SHEET 32 63

SHEET 33 63

SHEET 34 63

SHEET 35 63

SHEET BB 03

SHEET 38 63

Fig. 8d1

Fig. 8d2

Fig.8d4

SHEET 45 63

Fig. 9d1

SHEET 47 63

Fig.9d2

SHEET 48 63

SHEET 49 63

Fig.9d4

Fig. 9d5

Fig. 9d6

Fig. 9d7

Fig.9d8

SHEET 54 63

SHEET 55 63

SHEET 57 63

SHEET 62 63

## MULTI-CHIP CALCULATOR SYSTEM HAVING CYCLE AND SUBCYCLE TIMING GENERATORS

Related subject matter is found in the following co- 5 pending patent applications filed concurrently herewith:

S/N 346,392, filed Mar. 30, 1973 TI-5190 — CALCU-LATOR SYSTEM FEATURING RELATIVE PRO- 10 **GRAM MEMORY ADDRESSING**

S/N 396,902, filed Sept. 13, 1973 TI-5191 — CALCU-LATOR SYSTEM FEATURING A SUBROUTINE REGISTER

LATOR SYSTEM HAVING AN EXCHANGE **DATA MEMORY REGISTER**

S/N 397,185, filed Sept. 13, 1973 — CALCULATOR SYSTEM HAVING PRECHARGED ARITHMETIC LOGIC UNIT

S/N 397,048, filed Sept. 13, 1973 — CALCULATOR SYSTEM HAVING A CONSTANT MEMORY

S/N 397,181, filed Sept. 13, 1973 TI-5195 — CALCU-LATOR SYSTEM HAVING KEYBOARD WITH DOUBLE ENTRY PROTECTION AND SERIAL- 25 IZED ENCODING

S/N 396,959, filed Sept. 13, 1973 TI-5196 — CALCU-LATOR SYSTEM HAVING A PRECHARGED VIRTUAL GROUND MEMORY

S/N 396,901, filed Sept. 13, 1973 TI-5199 — CALCU- $^{30}$ LATOR SYSTEM HAVING MULTI-FUNCTION MEMORY INSTRUCTION REGISTER

S/N 397,465, filed Sept. 13, 1973 TI-5200 — CALCU-LATOR SYSTEM USING INSTRUCTION WORDS AS DATA

S/N 397,054, filed Sept. 13, 1973 TI-5287 — CALCU-LATOR SYSTEM HAVING PLURALITY OF PRO-**GRAM MEMORY ADDRESS REGISTERS**

This invention relates to calculator systems in general 40 and more specifically to addressing and timing relationships in multi-chip registers.

## TABLE OF CONTENTS

**BACKGROUND OF THE INVENTION** BRIEF DESCRIPTION OF THE DRAWINGS DESCRIPTION OF GENERAL BLOCK DIAGRAM DESCRIPTION OF BLOCK DIAGRAMS OF ARITH-METIC AND SCOM CHIPS

THE IDLE HOLD, AND COND COMMAND BITS INSTRUCTION/ADDRESS/CONTROL WORD FOR-MAT

TIMING

THE KEYBOARD INPUT MATRIX

THE KEYBOARD INPUT SYSTEM

THE KEYBOARD REGISTERS I/O CONTROL

REGISTERS A-E AS IMPLEMENTED IN A SAM

THE PUSH/PULL MATRIX

ARITHMETIC LOGIC UNIT (ALU)

DECODING THE INSTRUCTION WORD

THE I/O CIRCUIT AND REGISTER 5

THE D TIME GENERATOR

THE DISPLAY OUTPUT CIRCUITRY

THE COND CIRCUIT

THE SCOM CHIP

THE HOLDING AND ADDRESS REGISTERS

THE F & G REGISTERS

THE MAIN ROM AND DECODER CIRCUITRY

THE S & D GENERATORS THE GATE CIRCUIT THE CLAIMS

#### BACKGROUND OF THE INVENTION

Electronic calculators have evolved from the desktop variety utilizing discrete integrated circuit packages to hand-held calculators utilizing complex MOS logic circuitry on one or more MOS/LSI chips. A calculator system adapted to be implemented using only one MOS/LSI chip is set forth in copending patent application, "Variable Function Calculator", Ser. No. 163,565, now abandoned and replaced by Ser. No. 420,999, filed Dec. 3, 1973, assigned to the assignee of S/N 397,056, filed Sept. 13, 1973 TI-5192 — CALCU- 15 this invention. A calculator system implemented utilizing a basic pair of MOS/LSI chips which is adapted for use with an expandable memory system for increasing data and program memory capacity is set forth in "Electronic Calculator", Ser. No. 255,856, now aban-20 doned and replaced by Ser. No. 360,984, filed May 16, 1973 and assigned to the assignee of this invention.

> As the consumer demands for hand-held calculators increases for systems providing more functions and more complex functions with increased memory capacity, the challenge to provide such a system with the minimum number of semiconductor chips, each with the minimum number of pin terminals has become major. For example, the standard MOS package for LSI chips contains 28 pins, and accordingly it is highly desirable to design complex calculator chips requiring only 28 output pins. Furthermore, because handheld calculators operate on battery power, and batteries, of course, only have a limited life, then designing the calculator chips system so as to provide minimum power dissipation is of paramount importance.

The electronic calculator system of the present invention fulfills the goals above enumerated in providing large scale semiconductor calculator chips in 28 pin packages by providing an addressing technique between the arithmetic chip and memory chip utilizing a multiplexed technique wherein various condition signals and addresses are communication on a single line in synchronization with cycle times and subcycle times. First cycle and first subcycle timing generators are sup-45 plied on the arithmetic chip and second subcycle and cycle timing generators are supplied on the memory chip, and the generators are synchronized during both cycle times and subcycle times by sending a condition bit to the memory chip at a particular cycle and subcycle time.

That is, one line between the chips is utilized for communicating to the other semiconductor chips, including the instruction memory chip, internal operating conditions such as whether or not the calculator is in 55 the calculating or idle mode. This condition is generated at a particular S time and D time for synchronizing the timing generators as well as for communicating the specific status information.

Another pin reduction technique utilized during 60 communication between the arithmetic chip and the memory chip is the multiplexing of various internal operating conditions of the arithmetic chip with a memory address on a single line to generate a multi-bit command word which is communicated to the memory 65 chip. Each bit of the command word is synchronized with a subcycle time, and a first set of bits represents internal calculator functions such as an unconditional

branch, hold or the inhibiting of the normal sequencing

of the instruction register, and a condition signal representing results of a test or status of a particular subsystem of the system. The second set bits in the command word represents a memory address only if a bit in the first subset is appropriately set.

### BRIEF DESCRIPTION OF THE DRAWINGS

The novel features believed characteristic of the invention are set forth in the appended claims. The invention itself, however, as well as further objects and <sup>10</sup> advantages thereof, will be best understood by reference to the following detailed description of the illustrative calculator system featuring an embodiment of the invention, when read in conjunction with the accompanying drawings, wherein:

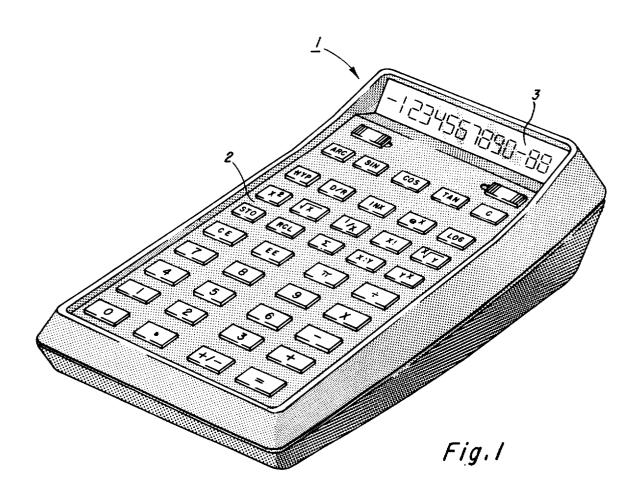

FIG. 1 is a pictorial view of the electronic portable calculator of the invention;

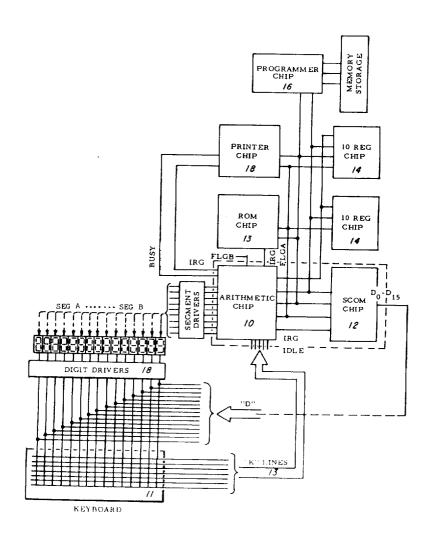

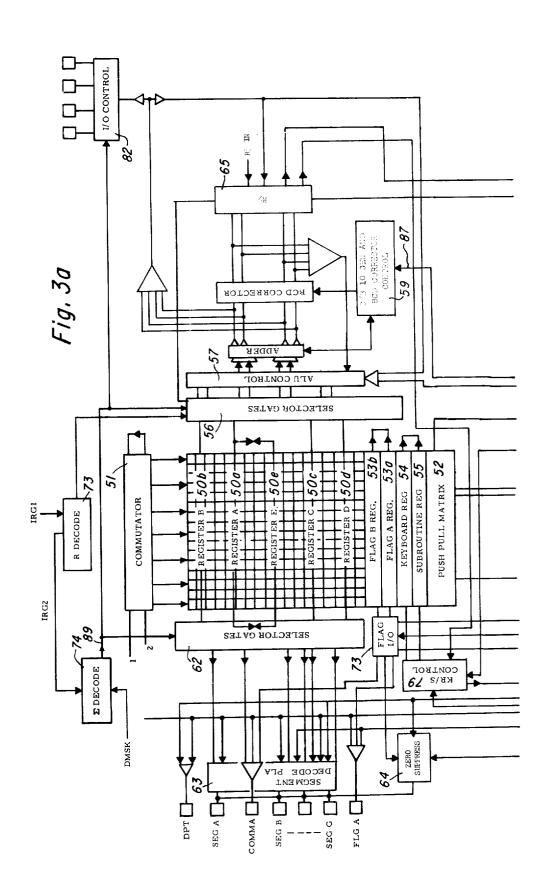

FIG. 2 is a simplified block diagram of the multi-chip calculator system of the invention;

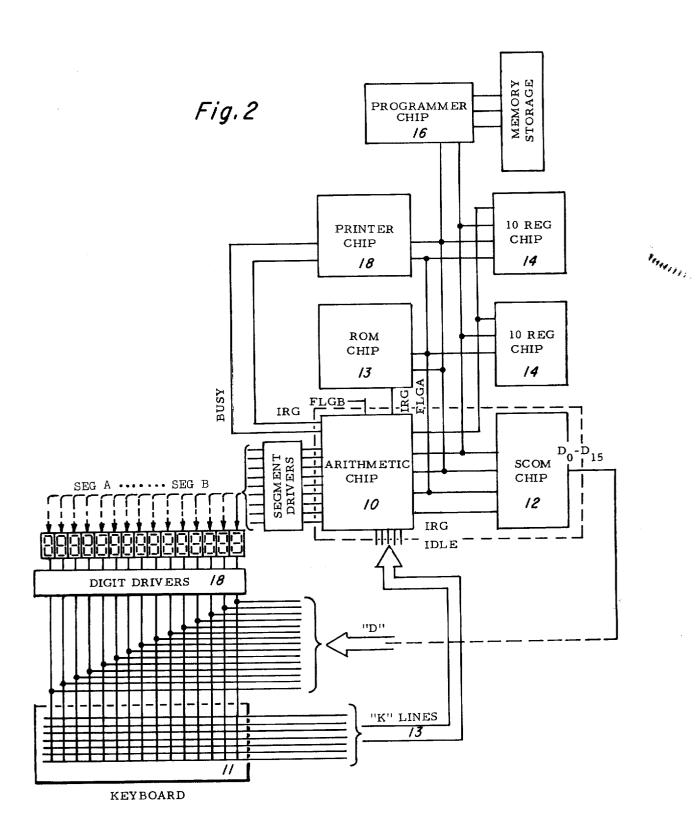

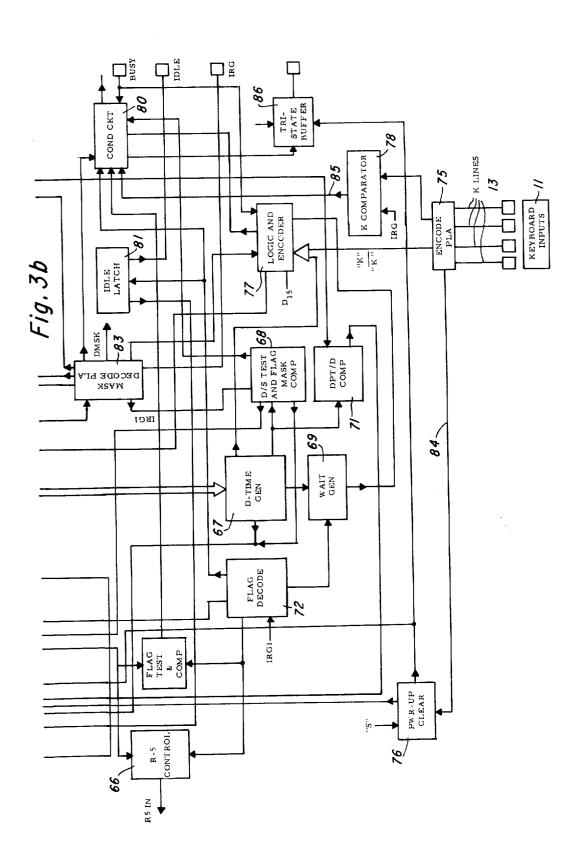

FIGS. 3a-3b are complex block diagrams of the arithmetic chip featured in this invention;

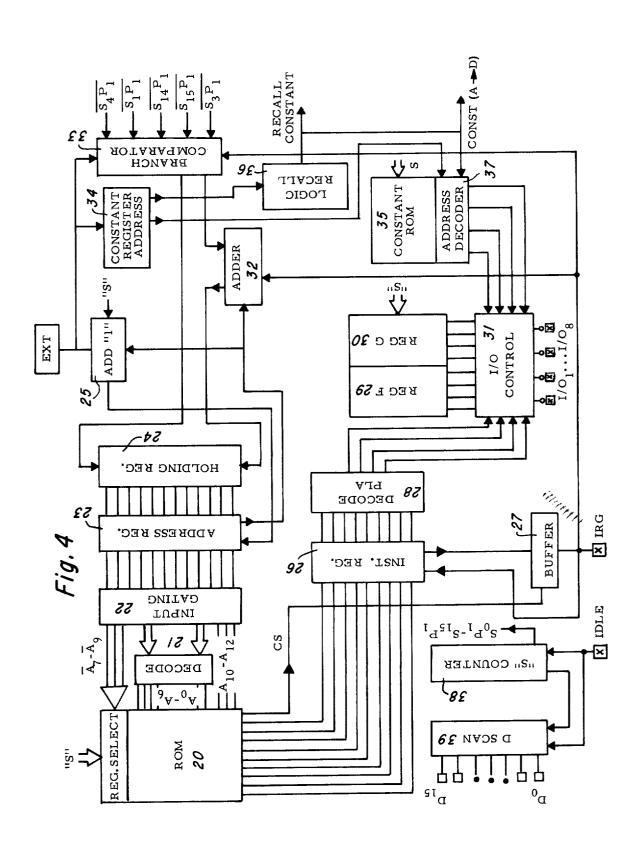

FIG. 4 is a complex block diagram of the SCOM chip featured in the electronic calculator of this invention;

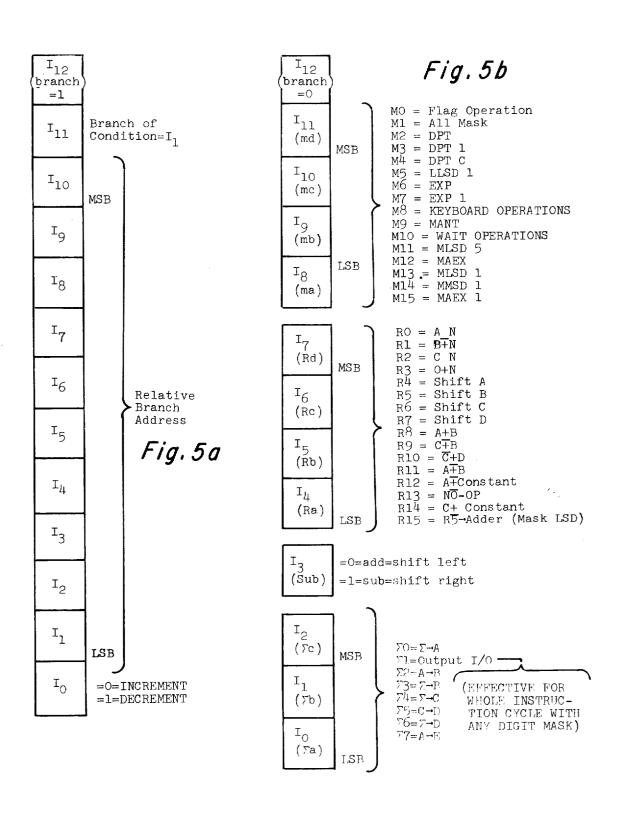

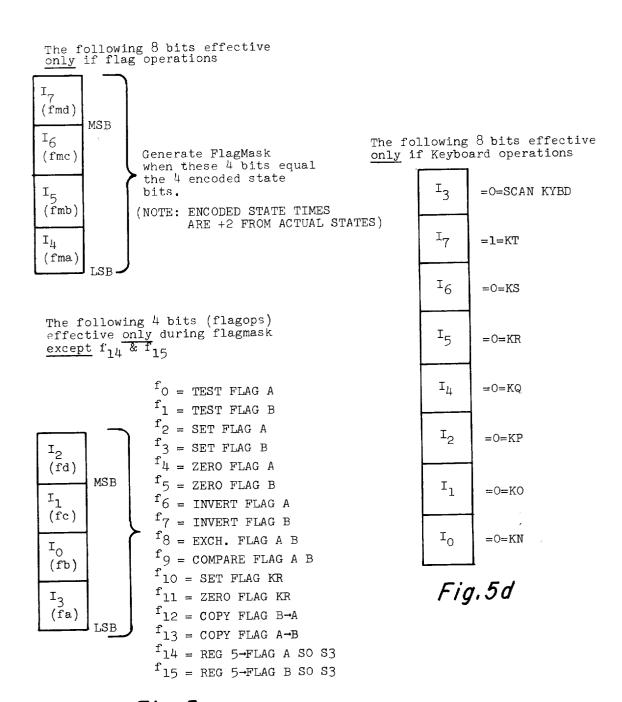

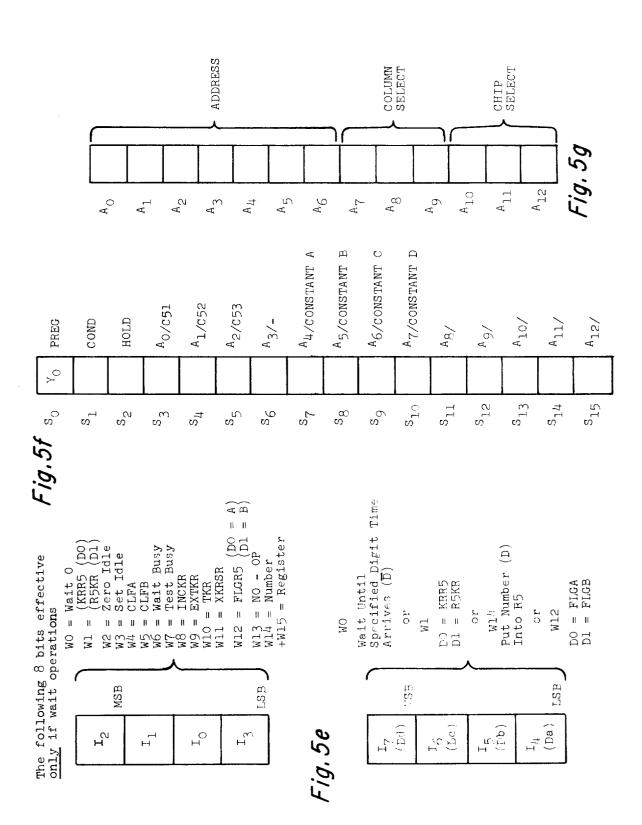

FIGS. 5a-5e are representations showing the coding of the instruction word used in the system of the invention; 25 tion;

FIG. 5f shows the decoding of the EXTERNAL signal;

FIG. 5g shows the ROM address as stored in the address register;

FIGS. 6a-6b are timing diagrams showing the timing of various parts of the system of the invention;

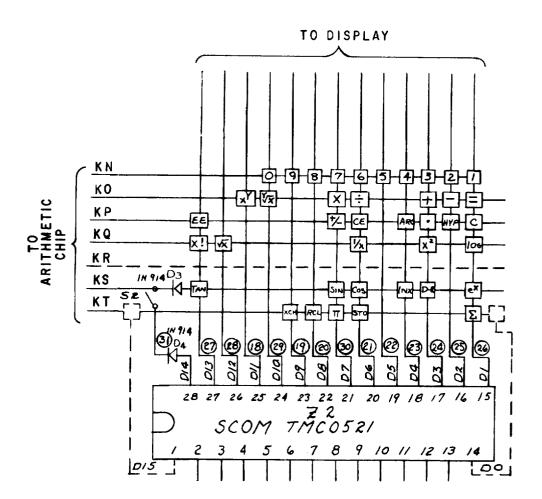

FIG. 7 is a representation of the keyboard input matrix;

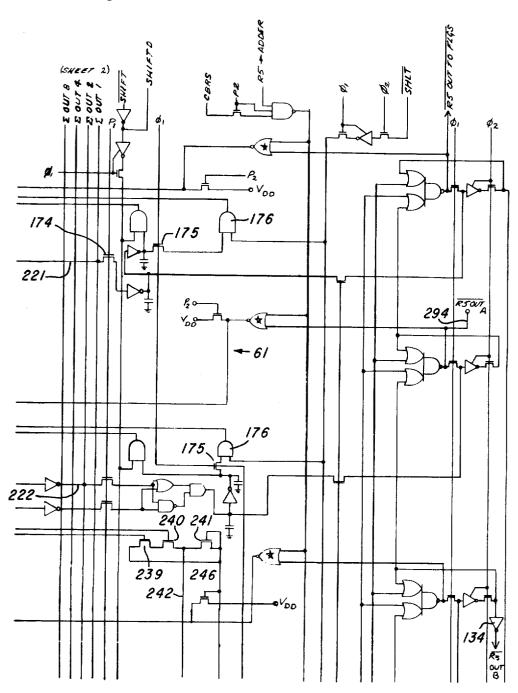

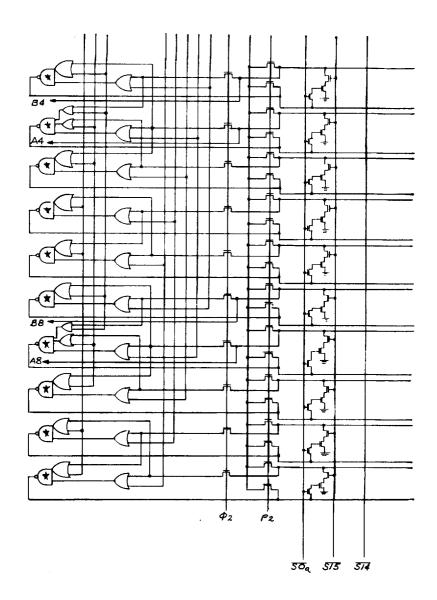

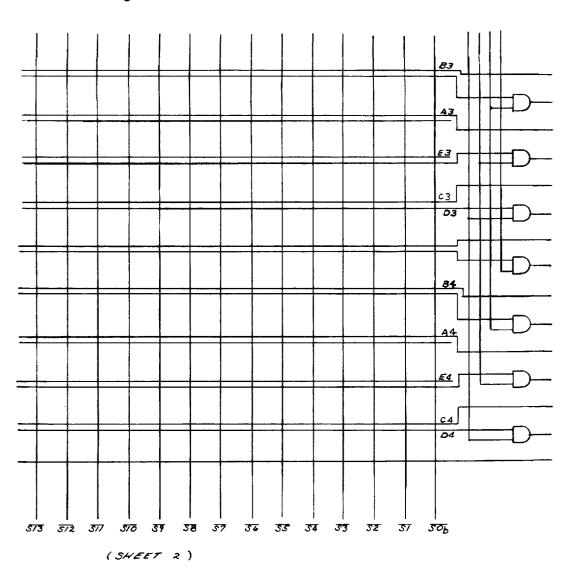

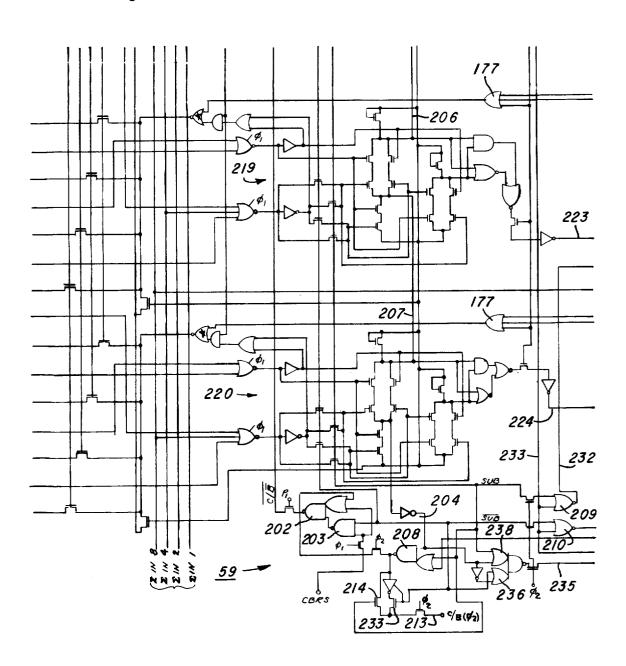

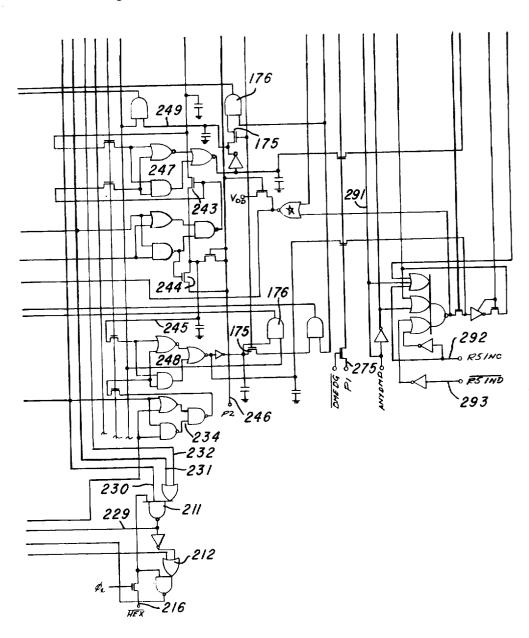

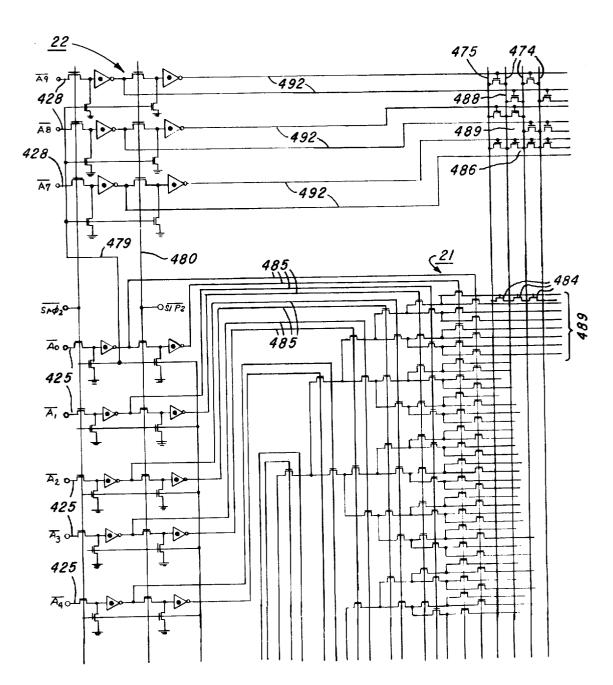

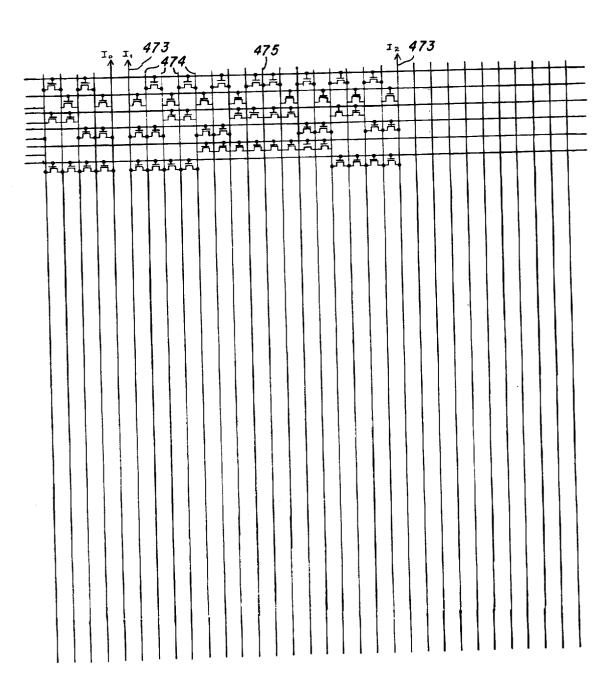

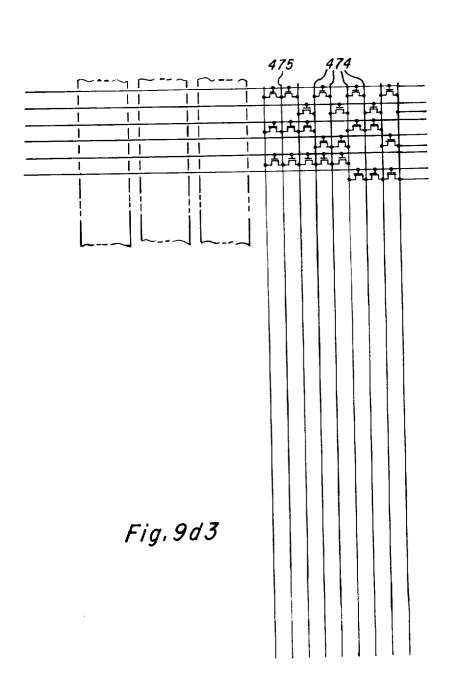

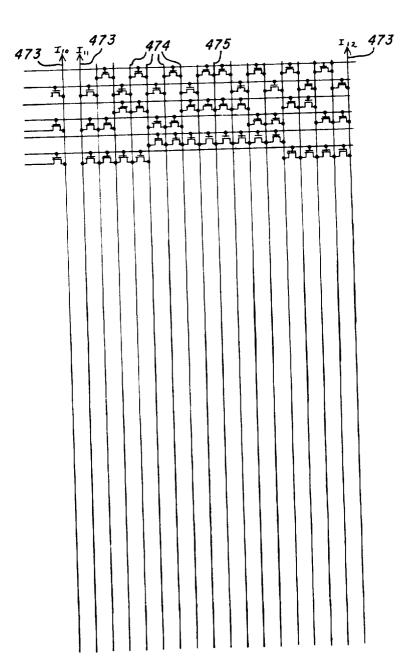

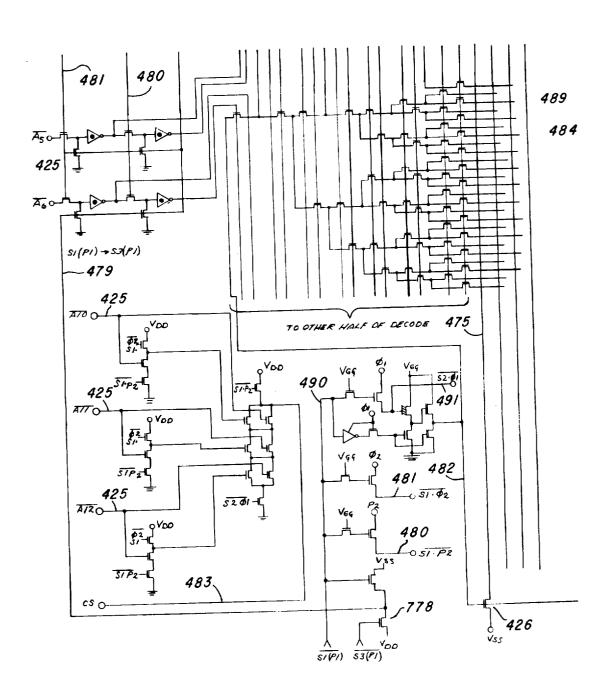

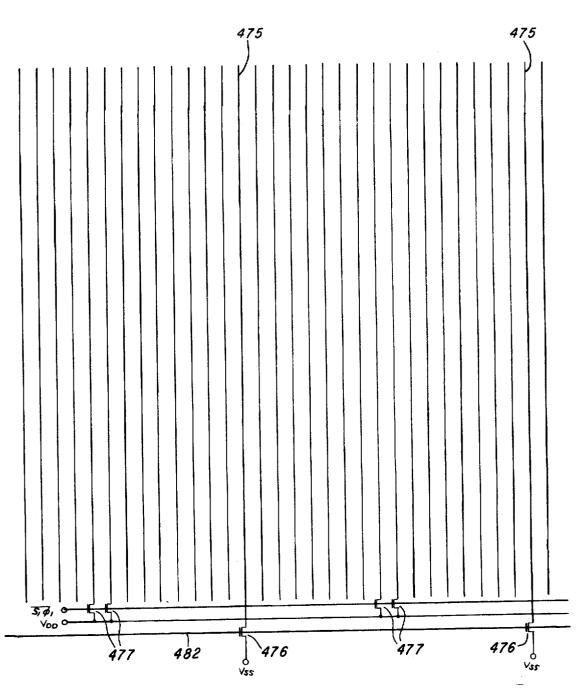

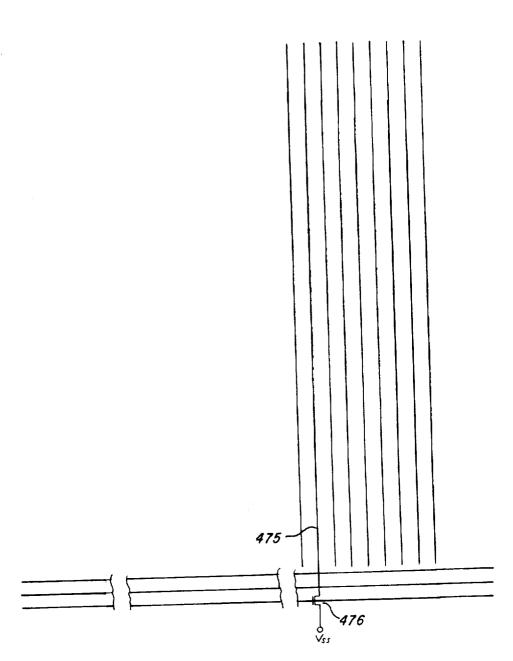

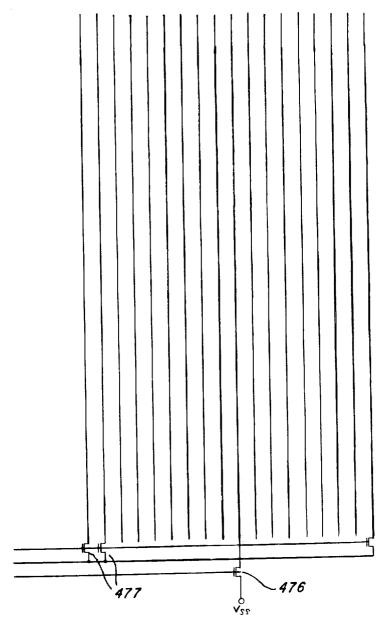

FIGS. 8a-8d are a composite schematic diagram of <sup>35</sup> the circuit of the "arithmetic chip" part of the system of the invention;

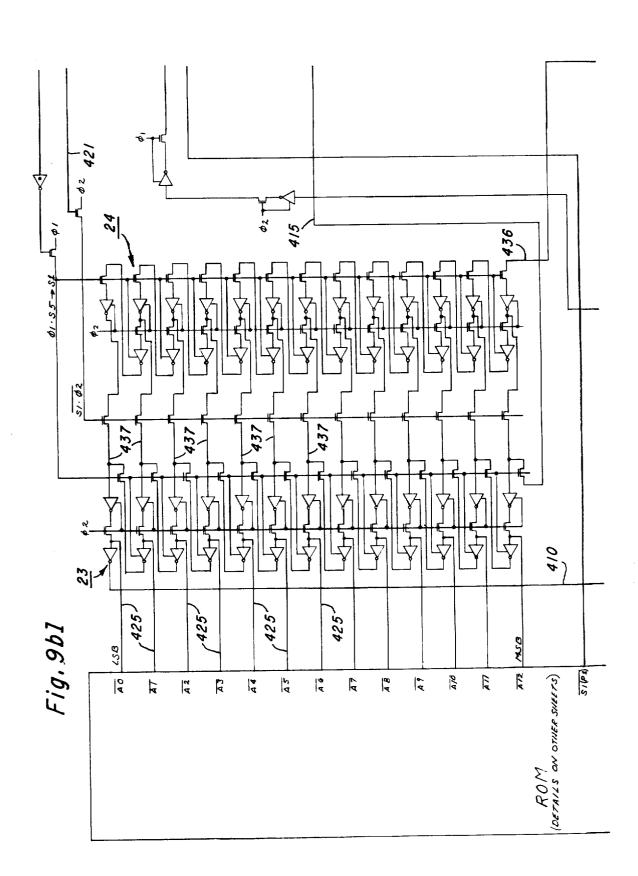

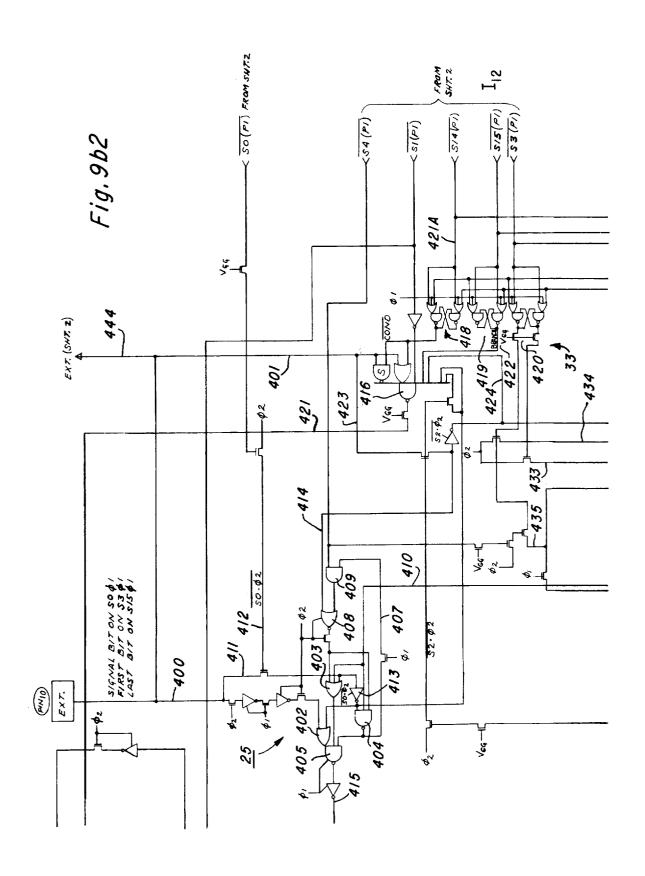

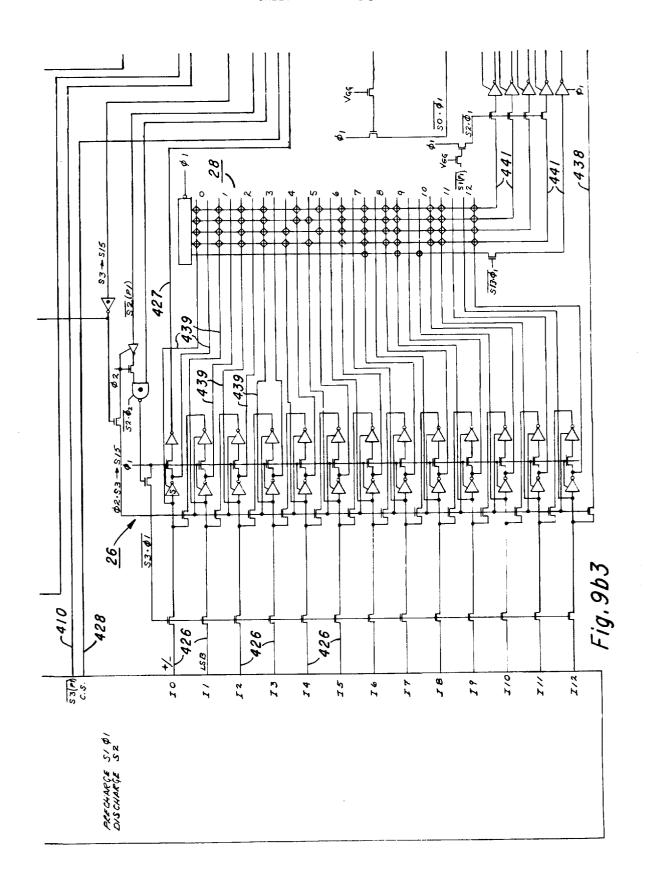

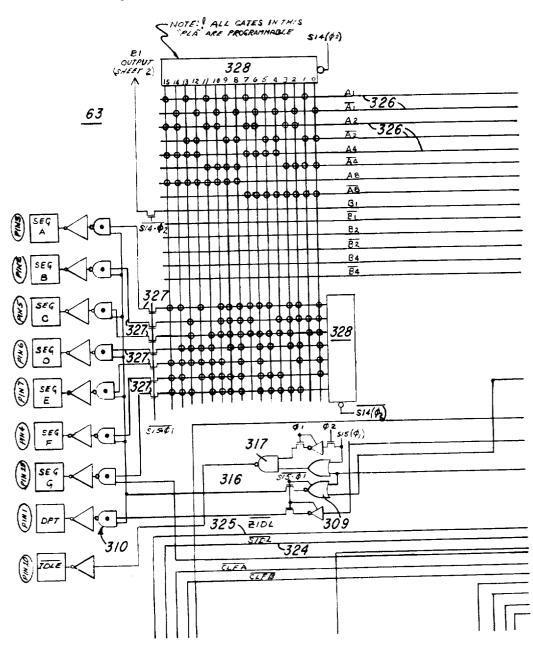

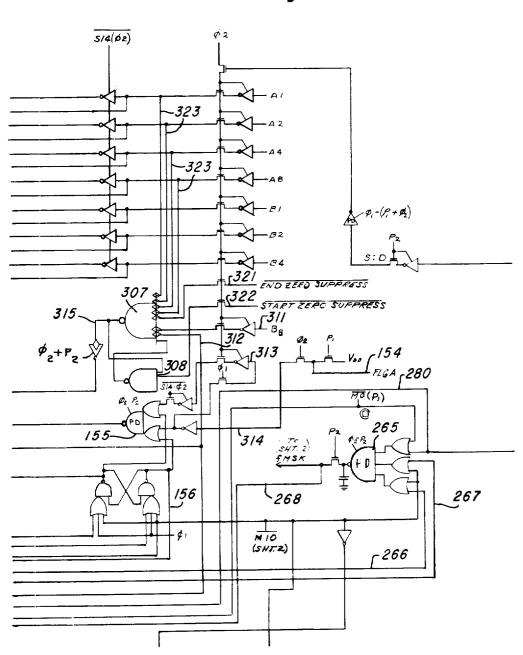

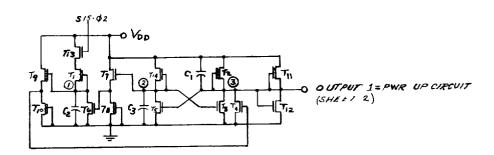

FIGS. 9a-9e are a composite schematic diagram of the circuit of the "SCOM chip" part of the system of the invention; and

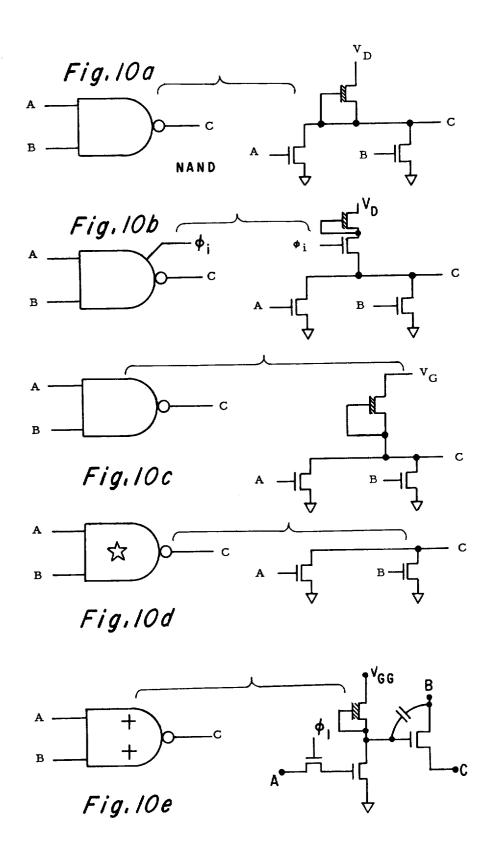

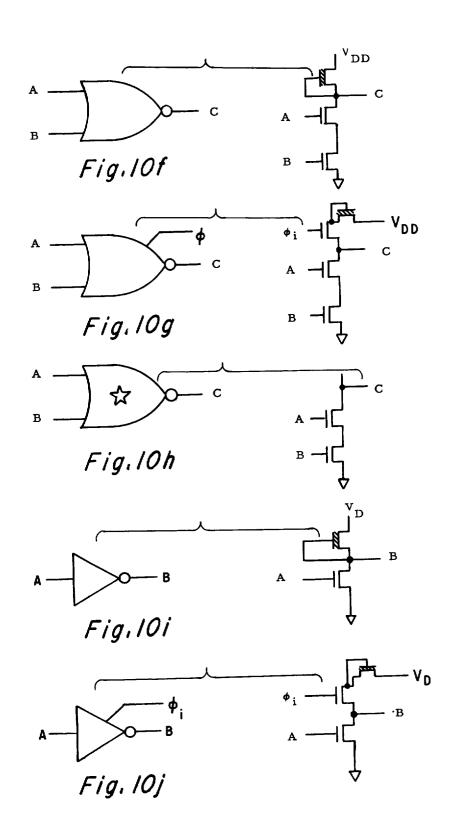

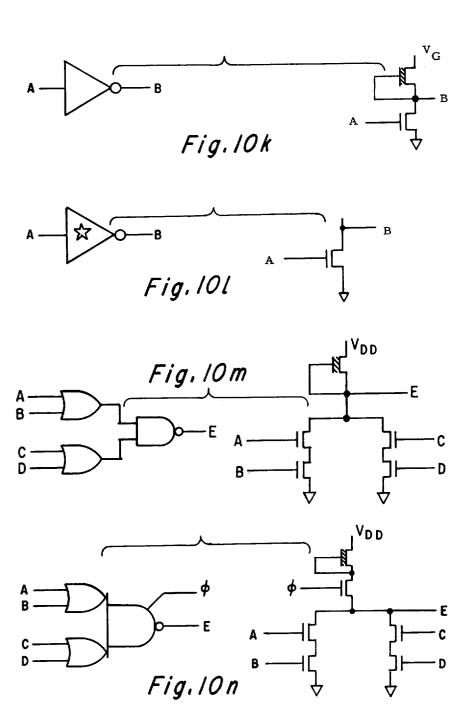

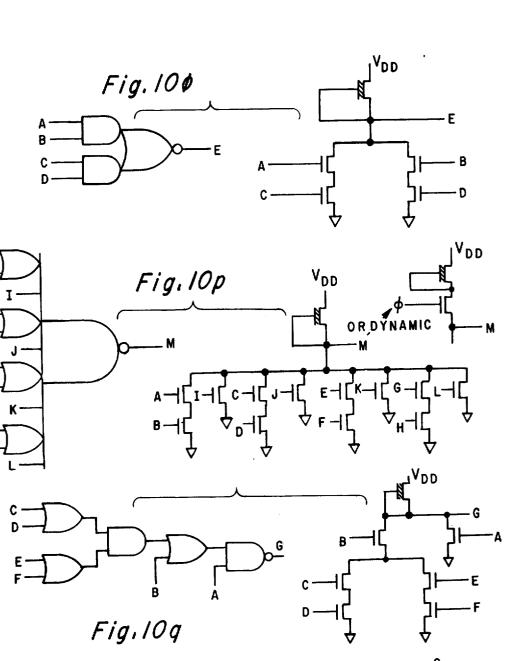

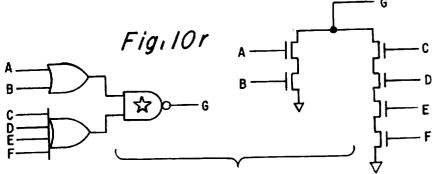

FIGS. 10a-10r are detail views of certain circuits used in the system of FIGS. 9 and 10.

# DETAILED DESCRIPTION OF SPECIFIC EMBODIMENT

Referring to FIG. 1, an electronic portable calculator 1 of the type which may employ features of this invention is shown in pictorial form. The calculator 1 comprises a keyboard 2 and a display 3. The display, in one embodiment, consists of fourteen digits or characters, 50 each provided by a gas discharge tube, a liquid crystal display unit, an array of light emitting diodes or other display means. The display is preferably implemented using scientific notation, allowing display of ten significant digits. Ordinarily, the display would be of the so- 55 called seven segment or eight segment variety, with provision for indicating a decimal point for each digit. The calculator system of this invention is adapted so as to provide a printed readout, if desired, using either thermal printing techniques or drum printing tech- 60 niques. The keyboard 2 includes a set of number keys of zero through nine, a decimal point key, and a plurality of function keys including exponential, logarithmic and trigonometrical functions. The exponential and logarithmic function keys include X2, the square root of 65  $X (\sqrt{X})$ , the reciprocal of X, (1/X),  $E^X$ , the log to the base 10 of X, (LOG) and the natural log of X, (1n X). The trigonometrical functions include the arc sine, arc

4

cosine and arc tangent of X, the sine, cosine and tangent of X, and the hyperbolic sine, hyperbolic cosine, and hyperbolic tangent and arc hyperbolic sine, arc hyperbolic cosine and arc hyperbolic tangent. Other function keys include the store, (STO), and recall, (RCL), keys are respectively storing and recalling a number in/from the memory registers in the SCOM chip. The enter exponent, (EE) key, allows exponent entry of the number displayed in scientific notation. A +/- key is provided for changing the sign of the displayed number. An exchange key, (X:Y), is provided for exchanging operator and operand in an arithmetic function. Other more conventional keys are supplied including the clear all key, (C), the clear entry, (CE), and the +, -,  $\times$ ,  $\div$ , and = keys. A sigma key,  $\Sigma$ , allows incrementing a number stored in the memory register directly. An X factorial key, (X) is provided as well as a degrees to radian/radian to degrees conversion key, (D/R), and a degrees/radian switch to set the calculator for operation in either degrees or radians.

Referring now to FIG. 2, there is shown a functional block diagram of the multi-chip calculator system of this invention showing the arithmetic chip and SCOM (Scanning and Read Only Memory) chip, hereafter described in detail, interconnected with peripheral chips providing expanded calculator capacity and capability. This invention is principally directed however to the arithmetic and SCOM chip pairs enclosed in the dotted lines 15, which chip pair provide one operable system without the peripheral chips. The arithmetic chip 10 generates a plurality of control signals to the SCOM chip 12, to an external ROM chip 13 providing for increased instruction word storage capacity, to the external multi-register chip set 14 providing external data word storage capacity, to the external programmer chip 16 providing a means for programming specific subroutines in the calculator externally, and to an external printer chip 18 for controlling an output printer responsive thereto (not shown). The output printers 40 may be of conventional design with adaptions to the printer chip 18, but preferably are of the thermal printer type or the drum printer type.

The control signals generated by the arithmetic chip 10 include the control signals:

EXTERNAL (EXT) indicates that the arithmetic chip is addressing SCOM storage and indicates which ROM storage (constant or program) is being addressed, and further communicates in multiplexed bit fashion the HOLD and COND control signals:

The HOLD bit in EXT indicates that an interrupt is desired in the normal sequencing of the ROM in the SCOM to allow additional executions by the system before the next instruction word is to be executed;

The CONDITION (COND) bit in EXT indicates that a condition latch has been set indicating status of a particular flag or the results of a comparison of flags;

IDLE (IDLE) is indicative of the idle condition of the data chip, i.e., whether the data chip is actually in the calculating mode (non-idle) or in the display or scanning mode (idle), and provides synchronization of the timing generators of the SCOM to the timing generators of the arithmetic chip;

Flag A (FLGA) is the serial output of the Flag A register in the SAM at an output rate determined by COND;

Flag B (FLGB) is the serial output of the Flag B register in the SAM of the arithmetic chip or is the B1 or first bit of the B register output.

Segment (SEGA-SEGG) is the data output of the Data Registers for actuating the seven segment display per digit to indicate a 0-9 numeral per digit according to the D times.

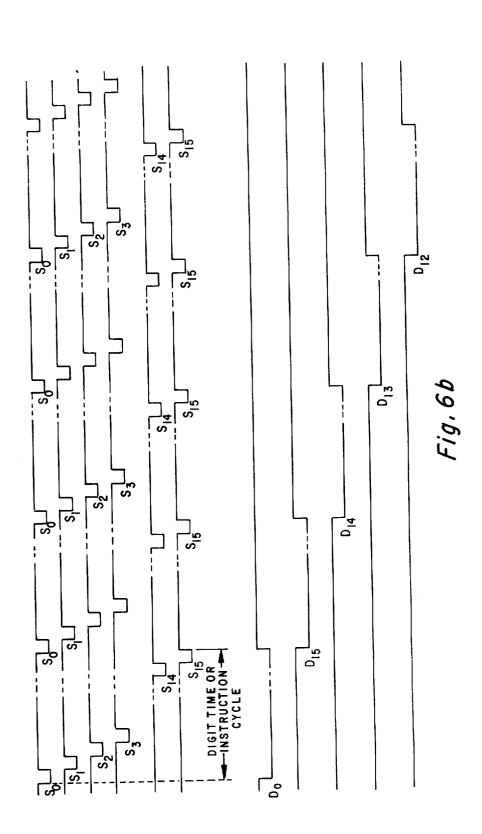

Display Time (D time) comprises timed signals 1 <sup>5</sup> each an instruction cycle of sixteen S times duration, wherein the D times are generated in cycles of sixteen so that D times precess from the particular D time of the preceding cycle;

Keyboard Inputs (K lines) are signals from the keyboard for entering externally commands to the arithmetic chip:

Instruction Words (IRG) indicate the particular instruction word comprising thirteen bits  $(I_0-I_{12})$  stored in a particular SCOM memory storage unit;

Busy (BUSY) represents the condition of peripheral chips such as the printer, as determined for example by the printer chip 18 that the printer is not/is busy and can/cannot receive another command for printing.

Input/Output (I/O) are data lines conveying data bits 20 from any of the various data registers and memories located in the arithmetic chip, SCOM chip, and 10-register chips.

Referring again to FIG. 2, the arithmetic chip 10 provides output data information from Registers B and/or 25 A and Flag Register A to the segment drivers 17. Necessary information which is provided is: position of the comma, position of the decimal point, actual data results to be displayed from the "B" and/or "A" register and data to be displayed from the Flag A register. The 30 segment drivers 16 comprise conventional driver circuits for actuating the above-mentioned displays 3, here shown to have a seven segment display plus decimal point per digit, with one digit actuated per D time. Thus for a 16 digit display in scientific notation driven 35 by 16 D times, there are up to 14 digits in the mantissa, 2 digits for the exponent, with 2 digits utilized as annotators for the mantissa and exponent being strobed non-exclusively.

The SCOM chip provides the D times to the digit 40 drivers 20 for selectively scanning in sequence the digits of the display 3 and the keyboard. Scanning of the display is explained in detail in the above-mentioned application Ser. No. 420,999. The D time strobing of the keyboard is set forth subsequently.

The SCOM chip 12 is responsive to EXT and IDLE command signals from the arithmetic chip and generates in response thereto the D times, the instruction word I<sub>0</sub>-I<sub>12</sub> (IRGA and IRGB) and data from the constant ROM on the I/O lines, all of which is communicated back to the arithmetic chip.

The ROM chip 13 depicted is one of the expandable set of peripheral chips allowing expanded calculator capacity. The ROM chip is responsive to the EXT and IDLE commands from the arithmetic chip for providing a 1024- additional instruction word capacity per additional ROM chip.

The multi-register chip 14 is another set of peripheral chips providing expanded data storage capacity of up to ten registers to the calculator system of this invention. The multi-register chip is responsive to Flag A, IDLE, and I/O information from the arithmetic chip for providing recall data through the I/O lines in return to the arithmetic chip.

The printer chip 18 is responsive to the I/O information from the arithmetic chip, the EXT, and IDLE commands from the arithmetic chip for printing in accordance with data on the I/O lines. If an impact printer

chip is utilized, the Flag A command is utilized from the arithmetic chip.

For minimizing pin count on the arithmetic and SCOM chips, and for maximizing silicon area utilization, both chips feature separate timing generators for providing S and D times, with the timing generator on the SCOM chip dependent upon the arithmetic chip for synchronization. Furthermore, instead of providing separate signals on separate lines between chips representing various conditions of the arithmetic chip, such as flags and sync signals, as heretofore utilized in earlier multi-chip calculator systems, the two-chip system of this invention features a multiplexed command signal from the arithmetic chip to the SCOM chip wherein each bit of a subset of bits in the command word represents the particular condition required to be transmitted. For example, the EXT signal communicated to the SCOM chip transmits a PREG (program register) signal in the So bit indicating that the SCOM chip is being addressed, transmits a second signal in the second bit at time S<sub>1</sub> for indicating the COND condition, and transmits the HOLD condition in the third bit at time S2 indicating that the ROM address register is not to be incremented. Heretofore, three separate signals and pins were required for transmitting this information. Although the arithmetic chip 10 and the SCOM chip 12 provide a basic operating calculator system as herein disclosed, the chip pair provides a basic system which anticipates adding peripheral storage and output function chips, preferably implemented in MOS/LSI utilizing novel methods of addressing for minimizing pin

Shown in FIGS. 3a-3b and FIG. 4 is a detailed functional block diagram of the arithmetic chip and the SCOM chip depicted in the calculator system of FIG. 2. A detailed description of the individual functional blocks will be discussed subsequently with regard to FIGS. 9 and 10, with only a general functional description of the basic "two-chip" system here set forth. It is understood that in the block diagrams of FIGS. 3a-3b and 4, a connection represented by a single line may represent a plurality of actual hardware interconnections, and for ease and simplicity of illustration, a single line may represent a plurality of different functions. The calculator system of this invention includes on the SCOM chip a main program ROM 20 responsive to decode and gating means 21 and 22, respectively, which selectively couple the address word in the address register 23 to the ROM for controlling which ROM location is being addressed. A holding register 24, in combination with an add-1 circuit 25, selectively generates a new ROM address in the register 23 when a branch instruction word has been executed. As will subsequently be discussed, branching will be implemented utilizing a relative technique wherein, instead of conventionally jamming in a complete new address, the old address will be incremented positively or negatively by a relative numerical amount to generate the new address.

An instruction register 26 is responsive to the output of the ROM 20 for storing the instruction word  $I_0$ – $I_{12}$  which enters the instruction register 26 in parallel. Thereafter, the instruction word is serially communicated to the arithmetic chip through the output buffer 27 which is under control of the ROM 20. A decode PLA 28 is responsive to the instruction register 26 after the instruction word has been transmitted through the buffer 27 and re-entered into the instruction register 26. Then the decode PLA 28 decodes the instruction

6

word providing store and recall commands to the registers F and G, 29 and 30, respectively, and to the constant ROM 35, through the I/O control circuit 31.

After the instruction word leaves the buffer 27 for transmission to the arithmetic chip, it is further communicated to the adder 32 and to the branch comparator 33, wherein, if the  $I_{12}$  bit of the instruction word indicates a branch is to be executed, the branch comparator enables the holding register 24 to accept the new instruction word from the adder 32, which adds a positive or negative increment to the old address storage received from the address register 23 to generate the new address.

The constant register address 34 is responsive to a command word EXT from the arithmetic chip for ad15 dressing a constant in the constant ROM 35 which provides up to sixteen 16-digit 4-bit constant words. Logic recall circuitry 36 couples the constant register address

34 to the address decoder 37 of the constant ROM 35.

Further implemented on the SCOM chip is an S 20 counter 38 and a D scan generator 39 for generating the S and D time timing signals of this calculator system, which D times D<sub>0</sub>-D<sub>15</sub> are outputed to the digit drivers and keyboard as shown in FIG. 2. Both generators are synchronized by a command from the arithmetic chip which command is synchronized with the D and S times on the arithmetic chip.

The arithmetic chip of FIGS. 3a-3b is generally responsive to the instruction word IRG from the SCOM chip and to external operator inputs from the keyboard 30 and other peripheral chips for executing the particular instruction word and performing the indicated arithmetic operation. The main data registers in the calculator system of this invention are Registers A-E, 50a - 50e, respectively. They are implemented in sequentially ad- 35 dressed memory (SAM) form which are driven by a commutator 51 which also drives a push-pull matrix 52 for generating timing signals. Also implemented in SAM format are four 1-bit registers utilized as two flag registers, Flag A, 53a; Flag B, 53b; the keyboard regis- 40 ter 54, a multi-purpose register; and a subroutine register 55. It is understood that although the term "register" is here utilized as descriptive of the SAM implementation, this is only a "black box" type description as internally there is no actual shifting of data. Accord- 45 ingly the SAM "memory" elements which are sequentially addressed are not "shift registers" in the literal sense. Data in Registers A-E, as will be discussed subsequently in detail, is acted upon by the adder circuit 55 as controlled by the selector gates 56, ALU control 50 57, carry/borrow generator and BCD corrector control circuit 59, and BCD corrector 61.

Selector gates 62 control exchanging and recirculation of Registers A–E. The calculator displays its results by outputting the contents of Register B and/or Register A, preferably Register A, and the Flag A register to drive the segment decode PLA 63 which provides the output display as shown in FIG. 2. Zero suppress circuitry 64 provides leading zero suppression so that only the most significant non-zero digit is first exhibited.

A fifth 1-bit register, Register 5, of four digits duration, is a multi-purpose register responsive to the output of the adder circuit 55, to I/O lines, and to the instruction word from the Flag Decode PLA 72 as controlled by R5 control 66. R5 control 66 provides control data inputs and control inputs to Register 5 responsive to decoded instruction information. A feature of this invention is the means allowing four bits of the in-

struction word to be entered into Register 5 upon the "NUM  $\rightarrow$  R5" command. Since Register 5 is coupled to the main SAM registers and to the ALU, such provision allows use of a subset of the instruction word as data for execution. Such a feature facilitates software generation of data required in various subroutines.

The push-pull matrix 52 provides timing information to the D time generator 67 which is a ring-tail counter to generate one D time or instruction cycle comprising sixteen S times. Generator 67 counts backwards from 15 to zero in cycles, causing the D times to appear to precess in sequence. The D/S Test and Flag Mask Comparator 68 is responsive to S and D times for generating sync pulses and masking signals for flag operations, respectively, and for setting COND circuit 80. The wait generator 69 is responsive to the D time generator and to a decoded instruction word from decoder 72 for generating a wait command to logic and encoder 77 for controlling keyboard scanning.

The decimal point/D comparator 71 is responsive to D times and to Register 5, 65, for generating a decimal point at the proper timing location and for ending zero suppress.

Decoding of the instruction words from the SCOM chip is done locally on the arithmetic chip. That is, the instruction words are initially decoded in the mask decode PLA 83 for generating masks to the arithmetic logic unit for communicating such information as decimal point location, mantissa, and exponent location. The instruction word is then communicated to the D/S flag mask comparator 68 and also to the flag decode matrix 72 which controls input and output of the flag registers 53a and 53b through the flag input/output control 73. The instruction word also is communicated from the mask decode PLA 83 to the R decode matrix 73 and then to the sigma decode matrix 74 for controlling the selector gates 56 and 62 for register selection/functioning.

External inputs are supplied to the arithmetic chip by a keyboard operator through the keyboard 11 via K lines to an encode PLA 75. A particular keyboard actuation commands to the hardware clear circuit 76 generates proper commands for initializing and resetting the calculator upon battery actuation. The encode PLA 75 provides encoded K line information to the logic and encoders 77 and to a K comparator 78. The logic and encoder 77 selectively supplies D time and K coordinates in serial form to the keyboard register/subroutine register control 79 for entry into the keyboard register 54. The K comparator 78 allows determination that a specific K line was not actuated, or conversely determines which K line, by a process of elimination, was actuated. This information is communicated to a condition circuit 80 which is a versatile latch circuit responsive to a plurality of functions for providing status of various conditions at preselected times. Idle latch 81 is responsive to the flag decode PLA 72 and provides information to the display output controls that the calculator is or is not in an idle or non-calculating state for appropriately blanking the display. This information is further communicated to the idle terminal as indicated for transmission to the SCOM chip for synchronizing the S and D generators there.

Another important feature utilized in the calculator of this invention is a technique utilized in reducing power dissipation on the chips by utilizing depletion loads for the decode circuits. That is, the decode circuits such as decoders 28, 72, 73, 74 and 83 are imple-

mented as programmable logic arrays, now well-known in the art, which utilize load devices implemented in depletion mode MOS. To achieve optimum levels of power dissipation, the loads are periodically clocked as needed soas to dissipate power only when needed during the cycle.

For clearer understanding of the novel, useful and unobvious features of this invention, a more detailed functional interrelationship of the above circuit components follows.

The program memory 20 comprises a novel 13 × 1024 ROM for storing the control program and advantageously features virtual grounding, a novel method of precharging, and a novel layout pattern reducing the number of ground lines. By implementing a virtual 15 ground ROM as the program memory, significant power reduction and silicon economy are achieved.

Instruction words I<sub>0</sub>-I<sub>12</sub> are read out of the ROM 20 one word at a time in bit-parallel into an instruction register 26 which functions as a parallel-to-serial con-  $^{20}$ verter for serially communicating the instruction word to the arithmetic chip through the buffer 27 on the IRG line. Buffer 27 is controlled by the ROM 20 via the chip select, CS, line which indicates that the particular ROM 20 has indeed been addressed allowing the in- 25 struction word read out of the instruction register 26 to be communicated to the data chip. Otherwise, an instruction word from another ROM on another chip, for example, the ROM chip 12 would be exported under control of its CS. When buffer 27 has been enabled by  $\ ^{30}$ the chip select line, the instruction word is transmitted on the IRG line to the data chip and is thereafter reentered into the instruction register 26 to be subsequently decoded by decode PLA 28. Such a re-entry and subsequent decoding is a feature of this invention, 35 whereby the multi-functional use of register 26, first as a parallel to serial converter of the instruction word, and then as a register for decoding the instruction word, reduces component and software requirements.

Furthermore, because the calculator system of this <sup>40</sup> invention is adapted to accommodate up to 8 SCOM or ROM chips, or any combination thereof, such a reentry and subsequent decoding allows the up to 8 ROM/SCOM memories to be coupled in parallel at the buffer 27 into the two-chip system with minimum control and timing requirements.

On the arithmetic chip, the instruction words from the ROM 20 are decoded locally in several decode PLA's, including the mask decode PLA 73 and the sigma decode 74, the functions of which will be subse- 50 quently discussed. Data is stored in registers 50 which are basically sequentially addressed random access memories organized as five data registers of sixteen digits each. Register E, 54c, although similarly implemented as Register A - Register D in a basic SAM con- 55 figuration, has no direct output terminals, functioning only to exchange its data with the data in the A register. The flage registers 53 and keyboard 54 and subroutine 55 registers are 16 bit registers, implemented as a SAM, each bit of which is separately programmable for 60 providing optimum utility. The keyboard register functions mainly to receive encoded controls from the keyboard for eventually interrupting and controlling the main ROM 20 on the SCOM chip 12. The subroutine register, like Register E, has no direct external outlet, 65 instead its function is limited to exchange with the keyboard register, functioning chiefly as a memory for storing program address during a jump instruction, so

10

as to remember the location to which control is to be returned after the subroutine has been executed. All operations on the data entered into the registers 50 is carried out in an arithmetic logic unit on the arithmetic chip which is of the bit-parallel, serial-digit type, and features a novel carry-propagate binary adder 55. The novel binary adder utilizes bidirectional IGFET switches for switching IGFET current sources to provide a binary adder especially adapted for MOS appli-10 cation in general and specifically in calculator ALU's. Exclusive-or circuitry conventinally utilized in the input and output circuitry has been eliminated by incorporating it into the adder logic itself to reduce required circuit size. The 4-bit register, Register 5, is responsive to the arithmetic logic unit and I/O control 82 and functions to store the decimal point location along with any other four bit number for entry into the A, B, C and D registers or into the adder. The BCD corrector 61 appropriately adds six (for addition) or ten (for subtraction) for correcting the output of the binary adder back into BCD.

Responsive to the instruction word from the SCOM chip, the sigma decode 74 and the R decoder 73 respectively control recirculate and exchange of the various registers and control which registers are coupled to the arithmetic logic unit (ALU). The mask decode PLA 83, in response to the instruction word from the SCOM, generates the appropriate mask for aligning the proper set of digits of the data word, such as the mantissa or the exponent, for operation thereon by the arithmetic logic unit.

The visual display 3 in FIG. 1 displays the contents of the B register and/or the A register in combination with the Flag A register. The segment decode PLA 63 is programmable such that either the output of the A or the B register may be decoded to drive appropriate segments in the display, and is programmable so as to accommodate up to 7 segments plus decimal point. A zero suppression circuit 64 provides suppression of the leading zeros so as to provide up to 10 digits of significant digits in a 12 digit display utilizing scientific notation. Suppressor 64 is responsive to the push/pull matrix 52 for beginning and ending suppression, and is also responsive to the decimal point generator and B register.

Inclusion of Register E in Registers 50 is a feature of the invention. Sigma decode matrix 74 controls the selector gates so as to allow exchange of Register E with Register A. Thus, the contents of Register E, although having no direct outlet, may be indirectly displayed via exchange with Register A or the contents may be aced upon by the arithmetic logic unit by exchange with Register A. Such a feature allows five registers to access a four input ALU, i.e., an N input adder addressed by N + 1 registers.

Another feature of this invention is the application of the subroutine register 55 in combination with the keyboard register 54 in a SAM configuration. Because the keyboard register functions mainly to address a specific location in the main ROM on the SCOM chip, the ability to store that location in, for example, the subroutine register via an exchange instruction, saves both hardware and software requirements. For example, by storing this information in the subroutine register, the keyboard register is free to perform other functions without endangering the loss of the memory address. Thus, when the subroutine has been executed and control of the program is to be returned to that address, another

exchange between the keyboard register and the subroutine register allows that address in the ROM chip to be directly addressed via the keyboard register upon a specific command "P Reg" which communicates a "1" at time So on the EXT line.

The "P Reg" command supplies both control instructions and ROm address on the external line in multiplexed format on the SCOM chip. This address accesses address register 23 on the SCOM chip which is capable of addressing each of the addressable locations  $\ ^{10}$ in the ROM 20, whereby the instruction stored in each location is read out into the instruction register 26. Usually the address register is incremented by one for each instruction cycle, as controlled by timing means and the ADD-1 circuit 25, so that the instructions of a 15 particular subroutine stored in the ROM are normally read out in sequence. However, branch instructions appearing at the instruction register 26 are recognized by the branch comparator 33 and interrupt the sequencing of the ROM address by a relative addressing method. 20 That is, the "old" ROM address is incremented positively or negatively in accordance with the instruction word from one of the ROM's available on either the SCOM or other external chip and the new location is stored in the holding register 24. For example, an incre- 25 mental address read out from the specific ROM location to the instruction register 26 and transmitted to the arithmetic chip through buffer 27 on line IRG is transmitted to the adder 32 along with an actuation signal from the branch comparator indicating a branch condition. The previous ROM address stored in the address register 23 is also communiated to the adder 32 via line 40 and the sum is transmitted via line 41 to the holding register 24. During the next instruction cycle, the new address word is read into the address register in parallel  $^{35}$ from the holding register 24.

The branch comparator 33 is responsive to the instruction word and to the command word from the arithmetic chip transmitted on the EXT line. If the  $l_{12}$  (or  $S_{15}$ ) bit of the present instruction word is for a branch, and if  $S_0$  is not a "1" allowing a "branch" possibility, and if the  $S_1$  digit bit thereof, the COND bit, matches the condition bit at  $S_{14}$  of the previous instruction word, then a branch results. If a COND match doesn't result, the address is incremented by one. The COND bit on the EXT line serves to indicate to the ROM that a special condition has been executed which may interrupt the ROM sequencing.

To address one of the constant registers in the constant ROM 35, or in one of the constant ROMs 35 if a plurality of SCOM chips are utilized in the system, the instruction word from the proper ROM 20 in one of the ROM/SCOM chips is communicated to the IRG pin and then communicated into all the instruction registers 26. The instruction word communicated to the arithmetic chip inhibits the S<sub>0</sub> bit to provide a logic 0 at S<sub>0</sub>. If the instruction is not for a branch as above explained, then the instruction word is decoded by decode PLA 28 to generate "recall constant" command. The command word from the arithmetic chip on the EXT line having a zero at S<sub>0</sub> is decoded in the constant register address circuit 34.

Upon a "recall constant" command received from the decode PLA 28 recall constant and constant A-constant D signals appropriately address the constant 65 ROM 35 for recalling one of the sixteen constants therein contained in sixteen, four bit constant registers. The constant ROM 35 comprises a  $64 \times 16$  (or  $16 \times 4$

× 16) unit array to generate the sixteen, 16-digit, 4-bit constants.

Decode PLA 28 also provides input/output controls to register F 29 and register G 30 which are additional data registers providing increased data storage suitable for memory storage under the operator's control. Data is stored into and recalled from the registers F and G, respectively, through I/O 1 . . . I/O 8 lines, in response to the decode PLA 28 which decodes the instruction word from the ROM. As explained with respect to "recall constant", the instruction word from the SCOM inhibits the  $S_0$  bits preventing "PREG". Only then will the F and G registers be addressable through decoder 28 as the I/O control 31 is under the control of the "recall constant" signal, which is generated in response only to the appropriate chip select signal.

Inputs from the keyboard 11 are entered into the arithmetic chip on seven keyboard lines or K lines 13 which are encoded into a 3-bit binary code by the encode PLA 75 for entry, along with the appropriate D time, into the KR Register 54. Data is entered into the encode PLA for an entire D time when a line is discharged, and then the lines are precharged awaiting a new code. As will be subsequently explained, because of the relatively long duration of a key depression on the keyboard as compared to the relatively high clock operating rates, a single key depression actuates the PLA 75 for sufficient instruction cycles to complete the routine called for; for example, upon expiration of one instruction cycle when the lines are discharged, the same keyboard entry is again reimpressed upon the decode PLA 75 for the next several instruction cycles upon the occurence of the respective D time of each cycle. The detailed explanation and description of the timing of the calculator system will be described hereinafter with regard to FIGS. 5a and 5b.

The K inputs are encoded by the PLA 75 and strobed into a K comparator 78 and into control logic and encoder 77. The K comparator 78 is also responsive to selected bits of the instruction word IRG which are programmed so that a comparison of the IRG bits and the encoded keyboard information provides information representing either that a specific K line has not been actuated, or provides information determining which K line has been actuated by a process of elimination. If a "match" is accomplished at the K comparator 78, the output thereof on line 85 causes the condition circuit 80 to set the COND latch, which setting has a predetermined meaning to the calculator at a particular S/D time combination.

The encoded K information is also communicated to the logic and encoder 77 which also selectively actuates the condition circuit 80 in combination with internally generated "wait" signals from the WAIT generator 69, and from the BUSY input terminal which communicates with other output chips, such as the printer. Upon a command from the flag mask generator 68, logic 77 allows the encoded K information to be serially combined with encoded D times and entered into the keyboard register 54 through the keyboard register/subroutine register control 79 in accordance with the condition of the COND latch and the WAIT generator. Shown in FIG. 3 is D time D<sub>15</sub> actuating logic 63 which automatically kicks the calculator out of a SCAN cycle if no keys are found actuated.

Thus, specific keyboard inputs, encoded as K line data and D time data, are loaded into the keyboard register 54. A "P Reg" command forces the ROM on the

SCOM chip to be addressed to a location as determined by the contents of the keyboard register.

The keyboard register provides functions other than addressing the main ROM and the constant ROM in the SCOM chip. For example, the tri-state buffer 86 on the external line EXT is controlled by instruction words so that data also may be entered onto the arithmetic chip as well as communicated from the arithmetic chip. Upon such an instruction, data on the external line such as from the programmer chip 16, may be entered 10into the keyboard register through the keyboard register control circuit 79. Another function of the keyboard register utilizes an instruction word which causes the contents of the keyboard register to be incremented by one, allowing it to function as a counter. If the number in the keyboard register represents an address of a constant in the constant ROM on the SCOM chip, then a succession of constants may be recalled during successive instruction cycles so that a subroutine may perform several iterations utilizing progressively smaller 20 constants according to an arithmetic progression. That is, since the keyboard register recirculates and has an add-one circuit, information therein may also be incremented by one, thereby providing a method for addressing constants in sequence in the constant ROM by 25 doing a succession of "recall constant" instructions with the keyboard register incremented by one each time. Utilizing the keyboard register in such an iteration technique is an important feature which allows implementation of the subroutine function with a mini- 30 mum of software requirements.

Four bits of the contents of the keyboard register also may be read into register R5 when a KR R5 instruction word is ordered. Because R5 is coupled into the registers A-D through the adder, then a number generated in the keyboard register may be inserted into the SAM memories for, for example, use in a software routine in the ROM requiring numerical data. By loading data in the keyboard register directly into the registers A-D in the SAM, instruction space in the ROM is saved in that otherwise a subroutine would be required to generate this data.

The instruction word I<sub>0</sub>-I<sub>12</sub> on lines IRG is comprised of a 3-bit sigma "S" field or selector gate field I<sub>0</sub>-I<sub>2</sub>, a 4-bit "R" field or register field I<sub>4</sub>-I<sub>7</sub>, a 1-bit "sub" or 45 subtract field I3, a 4-bit "M" or mask field I8-I11, and a 1-bit branch field  $l_{12}$ . At  $S_{15}$  after the instruction word has been serially clocked onto the IRG line which started at S3, the 4-bit M field of the instruction word and the  $I_{12}$  branch bit is decoded by the mask decode 50 matrix 83. The mask decode PLA functions so as to provide a "mask" for allowing manipulation of only a selected part of the data word, i.e., the mantissa or the exponent. This function is needed only when an instruction is commanded, as opposed to a branch, so the 55 mask decode matrix is only responsive to the M field when the branch bit is a zero. The mask decoder is further responsive to the push-pull matrix 52 which provides encoded state times, the decimal point and exponent timing information. The mask decode matrix pro- 60 vides an output signal DMSK or digit mask for providing the mask for the selector gates coupled to the sigma decode matrix 74. Also provided are masks coupled to the ALU control 57 for providing a mask for any particular part of the data word to be added. Line 87 pro- 65 vides control to the BCD corrector 59 for preventing improper carries out of certain mask fields. Bits I<sub>8</sub>-I<sub>12</sub> also generate a constant N as decoded by the mask de14

code PLA 83 for input to the binary adder, as controlled by the R field, bits  $I_4$ - $I_7$ , as decoded by the R decode 73.

At S<sub>13</sub>-S<sub>15</sub>, the 3-bit sigma field is clocked into the sigma decode matrix 74. The sigma field is decoded for selecting, transferring or recirculating data among the registers A-E. That is, lines 89 control the exchange of data between the A and B registers and between the C and D registers and controls recirculation of the A, B, C or D registers. The sigma field also controls the selector gates so as to allow entry of the Reg. 5 back into the adder via lines 88. Sigma control lines also control entry of the output of the BCD corrector 61 back into the SAM for right and left shifting.

The R or register decode matrix 73 receives the R field during  $S_6$ – $S_9$  of the instruction word which controls the selector gates 56 for determining what main register in the SAM is coupled to the ALU. Also, bits  $I_4$ – $I_7$  are generated to the K comparator 78 as earlier explained.

The flag mask comparator 68 receives the R field  $I_4$ – $I_7$  of the instruction word and compares it with the encoded S time for providing "FMSK" or "flag mask" when a flag operation is commanded. Output from the flag test and compare logic 68 is coupled to the COND condition circuit 80 as an indication that the condition exits that, for example, two flags are the same. The flag decode PLA 72 is responsive to the  $I_0$ – $I_3$  bits for generating flag register commands including recirculate, exchange, R5 to keyboard register, test flags and setting and zeroing idle latch. Bits  $I_0$ – $I_3$  are also decoded and supplied to the K comparator 78.

Operation of the A-E registers and the ALU is briefly as follows. Assuming data in the SAM register is awaiting operations, the instruction word subsequently is decoded into its M, R and sigma fields. If, for example, the instruction is for an add routine, the sigma field may cause the data in Reg. A to be entered into Reg. B, awaiting a second data input from the keyboard to be entered into the keyboard register which is then entered into Reg. A through Reg. 5 as above described. Under the control of the R field from the instruction word, the respective registers A and B are coupled into the ALU binary adder. The M field of the instruction word provides masks from decode PLA 83 supplying to the ALU the location of the decimal point, and what part of the word is the mantissa. Reg. 5 in response to the mask decode PLA 83 receives at the edge of the digit mask signal the output of the ALU which is the decimal point location. The mantissa part of the output word from the ALU is then coupled back into Reg. A through a BCD corrector 61 as needed. At a proper time the A Reg. is then outputed through segment decode PLA 63 to the display.

In displaying the decimal point information in Reg. 5, a routine generally utilizing the D time generator 67, the decimal point/D comparator 71 and the R5 register 65 is utilized. That is, as above described, R5 contains a number representing the location of the decimal point position. That number is coupled to the DPT/D comparator 71 along with the encoded D times.

When the D time representing the timing of the system matches the adjusted decimal point input, then at time S<sub>15</sub> the decimal point output at pin 1 is actuated for the duration of the instruction cycle by way of the idle latch circuit. A particular decimal point indicator on the display is energized during the particular D time at the desired location in the display in response to pin

1.

Another feature of this calculating system is the leading zero suppression of the display. The D/S flag test and mask comparator 68 provides a sample signal every instruction cycle when the S time encode and D time encode is coincident so that the time of occurrence of the sample signal is one of precession, i.e., S<sub>15</sub> of  $D_{15}$ ,  $S_{14}$  of  $D_{14}$ ,  $S_{13}$  of  $D_{13}$ , etc. because D times precess. This sample signal gates the segment decode PLA 63 which, coupled with a zero suppression gate 64, provides zero suppression of the most significant digit first. Suppressor 64 is responsive to the DPT generator for ending zero suppression upon occurrence of a decimal point, and zero suppress is ended by a bit communication from the B register during an EE entry. Also, the 15 Push/Pull matrix supplies Start/Stop zero suppression signals every D time.

The initial program which the calculator executes upon actuation by a user is the power up clear routine. The power up clear circuit 76 which clears and initial- 20 izes the calculator upon user initial actuation provides a first input to the external buffer 86 control circuitry generating a "1" at So and zeros thereafter on the EXT line. This is accomplished by setting the S<sub>0</sub> "flag" of the KB register and setting bits  $S_{3}$ – $S_{15}$  to zero in the KB reg-  $^{25}$ ister. The KQ input from the keyboard at time D<sub>15</sub> provides another hardware "clear" input on the EXT line for initializing the calculator. That is, upon power up, or a key down at D<sub>15</sub> on line KQ, the clear circuit 76 forces a "1" at time  $S_0$  to be outputed on the EXT out- 30 put line and causes zeros during the remaining S times. At time S<sub>0</sub>, the SCOM sees a 1 and realizes that the subsequent instruction during  $S_{3}$ - $S_{15}$  is an address which is zero. The ROM is thereby reset back to location zero and reads out of location zero an instruction word to 35 begin its initial sequencing.

## The IDLE, HOLD and COND Command Bits

Sequencing of "new" instructions coming from the ROM to the arithmetic chip at times are desirously interrupted. That is, if the calculator is waiting for a particular D time before executing the next instruction, the ROM must send out a succession of "WAIT" instructions. The ROM is then instructed to stop incrementing and for it to "HOLD" at its present location and to continue sending out the instruction stored in the instruction register location. To accomplish this, the old address in the address register is recirculated through an inhibit increment circuit. An example is during a keyboard scan requiring a complete D or instruction cycle.

On the standard programming of the two-chip system of this invention, the S<sub>2</sub> or "HOLD" bit is controlled by the presence of a wait instruction from wait generator 69 or the test/wait busy or test/scan decoded command 55 having its respective test condition fulfilled. These are commands for the ROM to stop incrementing at its particular location until reactuated by the data chip. During the "one" state of hold, the holding register 24 on the SCOM chip receives back the same previous in- 60 struction, which generates either the wait or the scan instruction. The same command is read back into the holding register as the "HOLD" signal inactivates the add-1 circuit 25 and the instruction register 26. The calculator stays in this recirculating loop until the presence of a  $D_{15}$  signal which changes the state of "HOLD" allowing entry of a new address into the address register and then a new address from the instruc-

tion register, as incremented, to be entered into the holding register. One example of such a wait or scan function is scanning of the keyboard where a wait until  $D_{15}$  is necessary. This ensures that the scan is started on  $D_{15}$  to assure scanning of all keyboard lines. Otherwise, if a scan started at  $D_{13}$  instead of  $D_{15}$ , remembering that the D times count backwards, a complete scan would comprise  $D_{13}$ – $D_0$ – $D_{15}$ , without scanning  $D_{14}$ . At the next time  $D_{15}$ , the calculator is kicked out of the wait/scan instruction as a hardware function at time  $D_{15}$  and a new instruction word is executed.

The signal "IDLE" communicates to external chips whether or not the data chip is in the "idle condition" and changes state at a predetermined S time and D time to synchronize the SCOM's timing generators. This synchronization is a feature of the invention as a separate sync signal and transmission line is not required, as in conventional systems. In the idle condition, the calculator's outputs to the segment terminals Seg A-Seg G and DPT are actuated at D time rate, and the machine is awaiting further information. When the calculator is not in the idle mode, it is actually computing, and the external display is blank except for the flag output which is displayed at S time rates. Thus, the idle output will either be in a high or low state representing a calculating/not calculating condition. Idle is responsive to the idle latch circuit, above discussed with respect to hold, which selectively actuates idle in response to instructions such as "set idle" or "zero idle" whether or not data is actually being operated on. For example, the idle "instruction" is utilized to transport synchronization information to the SCOM chip at D14S0 wherein the S counter 38 is synchronized at S<sub>0</sub> and the D scan generator is set at D<sub>13</sub> by respective edge detector circuits. By programming a "WAIT" D<sub>15</sub> instruction followed by a "set idle" the idle terminal transmits a level change of logic one to logic zero at D<sub>14</sub>S<sub>0</sub> (remembering that D<sub>14</sub> is the next instruction cycle after D<sub>15</sub> as D times precess). This is a feature of the calculator system which allows a one pin reduction of the conventional requirement.

Idle, in addition to providing idle conditions and sync timing, also performs other functions. That is, if flag condition information is being sent to other chips, Idle is utilized to indicate at what rate the flag information is being sent. That is, whenever data is being displayed, i.e., the calculator is in the idle condition, the flags are being sent at the same timing rate as the register information, i.e., one particular flag is transmitted during each instruction cycle or D time. This enables the flag to actuate functions such as decimal points, minus signs, or commas depending upon the specific program.

When the calculator is not in an idle mode, and Idle is in the "other" condition, the flags are being transmitted at state time rates; that is, one flag per state time or sixteen flags per instruction cycle or D time. The flag during this time may be utilized to selectively actuate other chips depending on whether or not a particular figure flag is set. Therefore, idle controls whether other chips will look at a particular flag by knowing whether or not the calculator is in idle.

The condition circuit 80 provides an output COND at  $S_1$  during the second bit of EXT for providing to the ROM a condition branch instruction. That is, if upon a particular test command the condition circuit and the COND bit is set and the  $S_{14}$  or COND bit of the branch instruction is also set, a new branch address generated and stored in the holding register is transferred to the

address register causing the ROM to jump or branch thereto. If the condition circuit is not set in relation to the S<sub>14</sub> bit, the next instruction word in sequence in the ROM is executed. For example, if the software routine requires a branch instruction when a particular flag is set, then at a particular time in the instruction cycle the flag is tested, and if the condition circuit is set in relationship to whether the flag was "set", then the ROM branches to the location of the desired routine. If the condition circuit is not set with respect to the flag condition, then the next sequential instruction from the original ROM location is executed.

The feature of a condition circuit and COND signal provides the machine the capacity of decision making dependent upon conditions which are under software 15 control increasing versatility. Other software controlled conditions which may set or reset the condition latch circuit is the depression of a particular key on the keyboard input, setting the latch. In response to this particular setting of the condition latch when a keyboard key is depressed, the keyboard scan is terminated. The condition latch is also set if, during any add or subtract operation, a carry out of the last digit of the register or a borrow out of the last digit is required. In other words, the condition circuit functions to indicate 25 an overflow condition. The condition latch may also be set upon a particular "test flag" operation, wherein if the flag is set then the condition latch will also get set and conversely.

The "busy" signal is an input to the arithmetic chip 30 which may be tested in a manner similar to that of testing a flag. For example, upon a "test busy" instruction, if there is an input on the busy terminal, software causes a setting of the condition circuit. If a printer chip is included in the expandable calculator system 35 herein described, it may be desirous for the calculator to stay in the idle mode until the printer chip has finished printing out the results. Then an input on the busy terminal from the printer chip indicates to the arithmetic chip that the printer is active and cannot take any 40 more data in to be printed. The arithmetic chip monitors the busy terminal and if a signal is thereon, the condition circuit will be set, allowing the calculator to perform a conditional branch to a particular wait condition until the printer is finished printing and ready to 45 receive more information. The busy terminal may also be used to create a "wait" condition until the signal subsides and also to provide feedback to the arithmetic chip as to the status of other peripheral chips such as the 10-register chip in addition to the printer chip in a 50manner similar to that above-described.

The input/output circuit 82 is used to both output data from registers in the SAM to external chips and to input data from the external chips to the data chip. Whether or not data is being input or output and to 55 which registers the data is channeled is under software control.

The Flag A, FLGA, output is utilized to display particular conditions of the calculator, such as error, arithmetic overflow, or entry overflow conditions. The output may also be utilized as a comma output which is stored in the Flag A register. Flag A is under control of the Idle signal and may be utilized for communication to other chips while the calculator is actually in the not idle or computing mode. As earlier discussed, in the calculating or not idle mode, the flags appear at the Flag A output once every given S time. This particular flag information is communicated to other chips, for

18

example, the 10-register chip, which in combination with idle directs the 10-register chip to store the conveyed data in a particular data memory therein. Utilizing the flags in this way is a feature of this invention as an almost unlimited amount of expansion is possible with peripheral chips in combination with the arithmetic and SCOM chips. The outputs labeled Seg A-Seg G are the outputs by which the 4-bit output code from the SAM registers is communicated to the display indicating which numeral is to be displayed. The two-chip system of this invention has segment decoding circuits 63 which may be programmed responsive to register B and/or to provide a programmable number of segments. That is, some types of displays require seven segments, as illustrated, to display the data.

The output labeled DPT is the decimal point output which is actuated at the particular D time responsive to the DPT/D generator 71 as controlled by Reg 5. No external decoding is necessary in the embodiment herein described, as the DPT output directly actuates the particular decimal point in the display.

The FLGB output terminal may also be utilized for outputting Flag B information. It is possible therefore in extremely complex systems using many peripheral chips wherein flags are used as means of controlling the chips, to output both sets of Flag A and Flag B. The Flag A output pin 11 has been discussed above. By outputing both Flag A and Flag B information, the amount of available control capacity is doubled. It is understood that in computer technology a flag is merely one binary bit indicating a preprogrammed condition which may be used to trigger circuitry.

## INSTRUCTION/ADDRESS/CONTROL WORD FORMAT

Shown in FIGS. 5a-5f are representations of the instruction word  $I_0-I_{12}$  as decoded by the various decode PLAs above-mentioned. FIG. 5a denotes the thirteen bit instruction word I<sub>0</sub>-I<sub>12</sub> as it appears in the instruction register 26 on the SCOM chip after it has been read out of the ROM 20. The formats for operations on branches (or increments) are different as seen in FIGS. 5a and 5b. The  $I_{12}$  bit is shown containing a "1" indicating that the instruction word is either an increment or a conditional branch command and not an instruction. That is, if bit I<sub>11</sub>, the COND bit, matches the COND bit of external communicated from the arithmetic chip at time  $S_1$ , then bits  $I_1$ - $I_{10}$  of FIG. 5a represent a relative branch address. That is, bits I<sub>1</sub>-I<sub>10</sub> represent an incremental number which is to be added or subtracted from the previous ROM location as commanded by the I<sub>0</sub> bit in FIG. 5a to generate a new address as shown in FIG. 5g. If the  $I_0$  bit is a zero, then the relative branch address in bits  $l_1-l_{10}$  is to be added to the old address. If  $l_0$ is a 37 1", then the relative branch address is to be subtracted from the old address.

If the  $I_{12}$  bit of the instruction word in the instruction register 26 is a zero, then bits  $I_0$ – $I_{11}$  represent an instruction which is decoded locally on the arithmetic chip and in the decode PLA 28 on the SCOM chip. For example, bits  $I_8$ – $I_{12}$  are decoded in the digit mask PLA 83 to provide the M or masking operations defined for an M field of  $M_0$ – $M_{15}$  and to provide a constant N. Bits  $I_4$ – $I_7$  are decoded by the R decode PLA 73 to provide the register or R operation indicated. Bits  $I_4$ – $I_7$  are also decoded in the D/S flag test and mask comparator 68 for providing FMSK as shown in FIG. 5c. Bits  $I_0$ – $I_2$  are decoded in the sigma decoder 74 for controlling regis-

ter select while the  $I_3$  bit actuates the logic and encoder 77 for indicating add or subtract. In FIG. 5c, the  $I_0$ – $I_3$  bits are decoded by the flag decode PLA 72 for generating the F or flag commands for controlling the flag registers. Decode PLA 28 decodes the instruction word for providing store and recall of the F and G registers.

Bits  $I_0$ – $I_7$  also actuate the K comparator 78 for determining which K line of the keyboard has been actuated upon a key depression. In FIG. 5e, bits  $I_0$ – $I_3$ , which are decoded in the flag decode PLA 72, also generate the wait or W instructions for placing the calculator in a non-operational or waiting condition until a specified condition such as the arrival of a specific D time encoded in bits  $I_4$ – $I_7$ . Bits  $I_4$ – $I_7$  are decoded in the flag 15 mask comparator 68 for generating the condition whose occurrence controls wait.

In FIG. 5f, the external command EXT is generated from the data chip in performing a "P Reg" or constant ROM recall. In bit  $S_0$ , the "P Reg" command with a 20"1" therein represents the condition that the arithmetic chip is desiring to jam in a specific address into the ROM for causing an unconditional jump, such as at power up clear. A zero in bit S<sub>0</sub> represents the conditions that the arithmetic chip may be either addressing the constant ROM, executing a conditional branch or merely communicating COND and HOLD signals. The P Reg jam-im circuitry is inactivated during constant recall allowing the ROM to increment normally. The second bit, occurring at time S<sub>1</sub>, is the COND bit for communicating to the SCOM chip the status of the condition latch, indicating that a conditional event has occurred to which the ROM should respond. The COND bit at time S<sub>1</sub> controls whether or not a conditional branch is executed as determined by the most recent instruction word from the ROM. That is, if the S<sub>1</sub> bit of external matches bit I<sub>11</sub> of the branch instruction, then the ROM will be incremented by the relative branch address as earlier discussed.

The third bit of external, occurring at time  $S_2$ , is the HOLD command indicating that the SCOM is to inhibit the incrementing of the ROM and "HOLD" the ROM instruction word for a specified period. The HOLD bit is responsive, for example, to the "WAIT" generator  $^{45}$  69.

Bits  $S_3$ – $S_{15}$  are always specific absolute addresses. If the  $S_0$  bit is a "1", then the  $S_3$ – $S_{15}$  bits represent a specific address in the ROM to which it is to branch. If the  $S_0$  bit is a zero, then the  $S_3$ – $S_{15}$  address may be that of a constant location in the constant ROM 35 for doing a "recall constant" or a conditional branch to the specific main ROM location. Upon a "recall constant instruction", as decoded from the decode PLA 28, then the preceeding EXT communication with a zero at time  $S_0$  will recall the specific constant.

Depicted in FIG. 5g is the coding format for the ROM address word as stored in the address register 23 on the SCOM chip. As the 1024 13-bit instruction 60 words are stored in the ROM 20 in a  $64 \times 16 \times 13$  bit array, bits  $A_0$ - $A_6$  address the 64 rows of the ROM, while the  $A_7$ - $A_9$  bits address the 8 columns per row for selecting the proper column addressed. Bits  $A_{10}$ - $A_{12}$  represent chip select and are decoded so as to enable 65 buffer 27 so as to control whether or not the instruction word from the ROM 20 is communicated to the arithmetic chip.

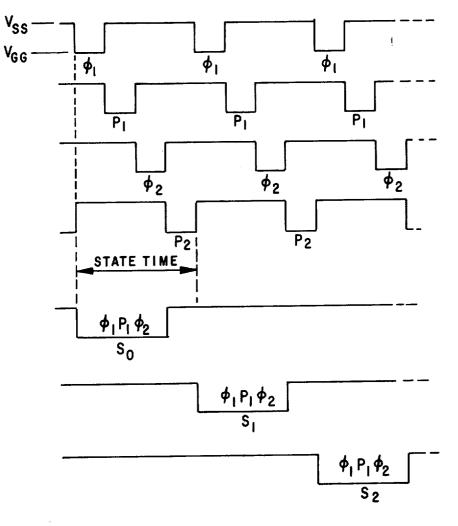

#### TIMING

The entire system operates on two externally provided clocks  $\mathbf{0}_1$  and  $\mathbf{0}_2$ , and two internally generated clocks  $\mathbf{P}_1$  and  $\mathbf{P}_2$ . The frequency used is 250 KHz for  $\mathbf{0}_1$ ,  $\mathbf{0}_2$ . The clock generators may be conventional and are not shown herein.

One set of clocks  $0_1P_1O_2P_2$  is referred to as a state time, and represents the time for one bit from each of the main registers A, B, C and D to be operated on in parallel by the ALU, etc. The BCD arithmetic used in the invention requires one full set of clock pulses for each digit, so sixteen sets or state times are needed to perform arithmetic operations on all 16 digits in a register. Sixteen state times represent one D time or instruction cycle, as seen in FIG. 6b.

Individual address lines in the registers 50-55 are energized only for three of the clocks  $\mathbf{0}_1$ ,  $P_1$ ,  $\mathbf{0}_2$ , rather than all four; these groups of three are also referred to as state times  $S_0-S_{15}$ . The same state times generated to operate the address lines of the SAM register 23 also operate or time the remainder of the system.

D times generated directly from state times  $S_0$ – $S_{15}$  are used to scan the keyboard and the display. As seen in FIG. 6b, the D times count down,  $D_{15}$ ,  $D_{14}$ ,  $D_{13}$ ... $D_{0}$  while the state times count up,  $S_0$ ,  $S_1$ ,  $S_2$ ... $S_{15}$ ; this feature aids in the zero suppression technique since leading zeros to be suppressed are on the left or MSD first while the ALU must operate from right to left or LSD first.

#### THE KEYBOARD INPUT MATRIX

In FIG. 7, there is seen a sixteen by seven matrix showing the keys from the keyboard arranged as scanned by the sixteen digit timing signals D<sub>0</sub>-D<sub>15</sub>, and as sensed on the seven outputs at KN-KT, from which keyboard information is entered into the system. If a "1" voltage appears on line KP at D<sub>13</sub> time, then the EE key is depressed, etc. The combination of a digit time and a sense line identifies a key, and these 16 and seven line items are binary encoded within the machine to appear as 4 and 3 bits respectively; TABLE 1A shows the format for loading keyboard and digit time information into the keyboard register 54, with the code of TABLE 1B being used for K information. If a key at D<sub>10</sub>, KP is down after a keyboard scan, the keyboard register will contain the word of TABLE 1c.

TABLE 1A

K<sub>n</sub> K<sub>b</sub> K<sub>c</sub> D<sub>s</sub> D<sub>4</sub> D<sub>2</sub> D<sub>1</sub>

LSB

| <del></del> |    |    |    |

|-------------|----|----|----|

| K - line    | Ka | Kb | Ko |

| KN          | U  | O  | O  |

| KO          | O  | 0  | 1  |

| KP          | 0  | i  | 0  |

| KQ          | 0  | 1  | 1  |

| KR          | 1  | 0  | () |

| KS          | 1  | 0  | 1  |

| KT          | 1  | 1  | 0  |

## DETAILED DESCRIPTION OF THE CIRCUITS THE KEYBOARD INPUT SYSTEM (FIGS. 8b5-6, 8h9-10

Keyboard of K information communicated from the KN-KT keyboard lines enters the data chip via pins 8-14. Bias elements 100 bias lines KN-KT to a logic 0 state so as to effectually precharge the lines in anticipation of signals from the keyboard. Precharge gates 101 precharge each of the lead-in lines from pins 8-14 at time S<sub>15</sub>O<sub>1</sub> through S<sub>15</sub>P<sub>1</sub>. A keyboard scanning technique similar to that set forth in "Expandable Function Electronic Calculator", Ser. No. 255,856, copending 20 herewith, strobes the keyboard lines in accordance with D times to provide the signals entering on pins 8-14. Each line is strobed for one D time, and the input data appearing on lines KN-KT appears for one D

For convenience, description of the keyboard will be exemplified for line KN only, but it is readily seen that the other six keyboard information lines are structurally similar and operate in the manner described with respect to line KN. By precharging the lines 102 by 30 means 101 at time S15 to logic zero, the keyboard data is effectively entered into the input circuitry at the next succeeding S time, or So, with actuation indicated by a logic "1".

At time S<sub>0</sub>0<sub>1</sub>, inverted K information is entered into 35 the register 103 comprising three clocked transfer gates such that data is allowed to the PLA 104 at time  $S_0$  and remains there for one D time until time  $S_{15}$  for decoding. Data is decoded for an entire D time to allow time for executing the keyboard command. At time 40  $S_{15}P_2$ , the line 102 input to the inverter is discharged to circuit ground, clearing for the next input signal, and the line 103 is precharged to V<sub>DD</sub> awaiting the next input signal. The succeeding K line signal is typically the same signal, as a keyboard operator actuates a K 45 line for some 1000 instruction cycles per key depression.

Decode means 104 comprises a programmable logic array (PLA) used for generating a code indicating which specific K line was actuated on the keyboard. 50 Programmable logic arrays, which function as a NAND gate, are now well known in the art. Encoder 104 provides first and second sets of encoded output data,  $\overline{K}_A - \overline{K}_C$ ,  $K_A - K_C$ , generated as a logic NAND combination of selected  $\bar{K}$  lines. The first set is the logic complement of the second set, a feature which advantageously provides data for determining when more than one key on the input keyboard has been depressed during a D time, i.e., an error condition caused by simultaneously punching two keys. The KN line is seen as an input to 60  $K_A$ ,  $K_B$  and  $K_C$  for the K set and is not an input for the K set,  $\overline{K}_4$  is seen to be the logic combination of KN , KP. KR . KT.

One of the lines 107 from the storage circuit 103 generates on line 108 an output signal providing a hard- 65 ware clear signal. Although a contact is shown on each K line, they are programmable and only one will be implemented. At time  $S_0\theta_{\scriptscriptstyle 1}$ , this signal is gated into logic arrangement 110 via line 109, so that at D<sub>15</sub>S<sub>1</sub>, in re-

sponse to line 111, a zero is generated and gated to the keyboard register input circuitry for generating a 1 at  $S_0$  to be transmitted to the SCOM chip, indicating that an address is being transmitted through EXT during  $S_{\rm 3}$ . 15, which address is zero. Further, if a power up latch signal is received during initial powering up of the calculator, logic arrangement 110 similarly outputs a logic 0 for resetting the calculator by transmitting a "1" in the So bit of EXT, followed by a zero address.